Embed presentation

Downloaded 38 times

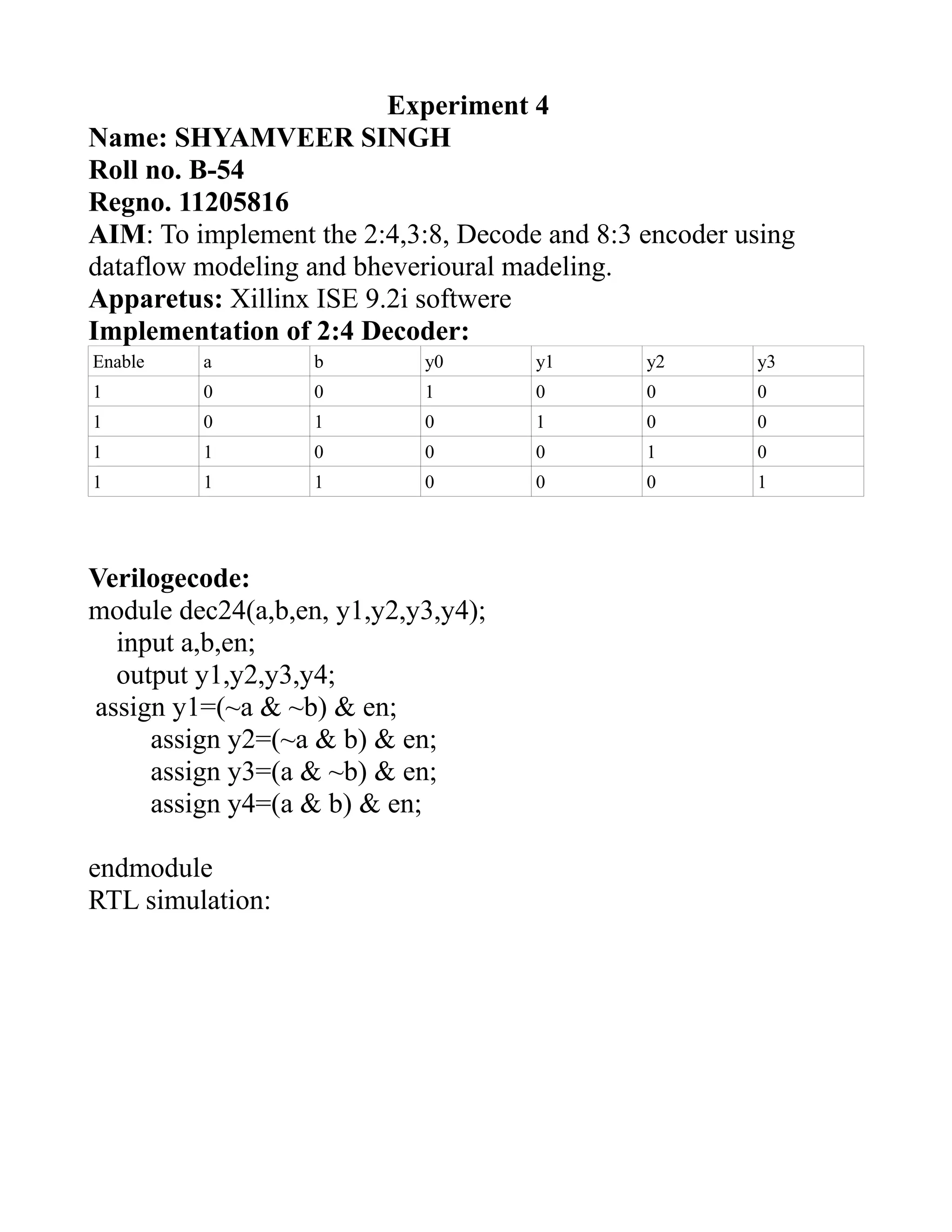

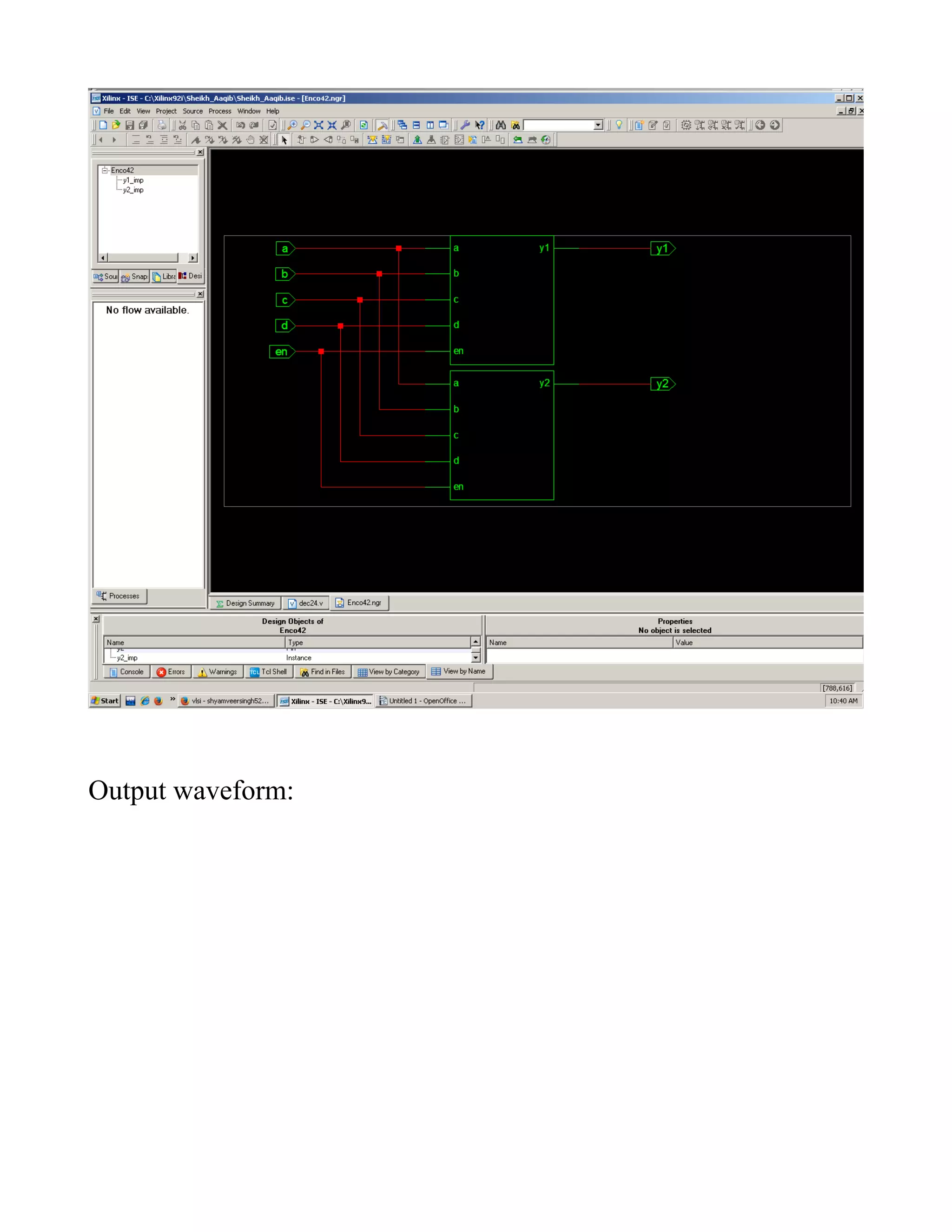

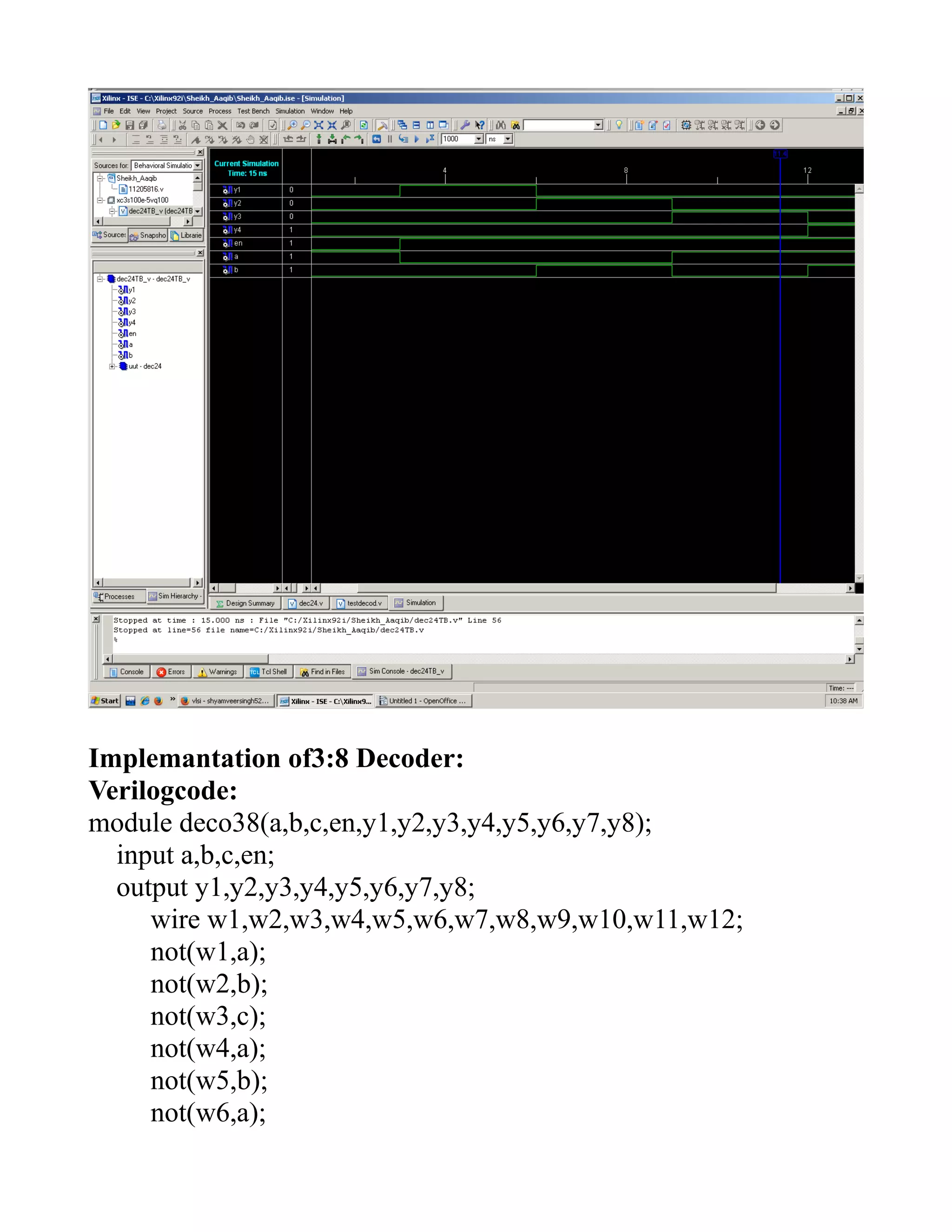

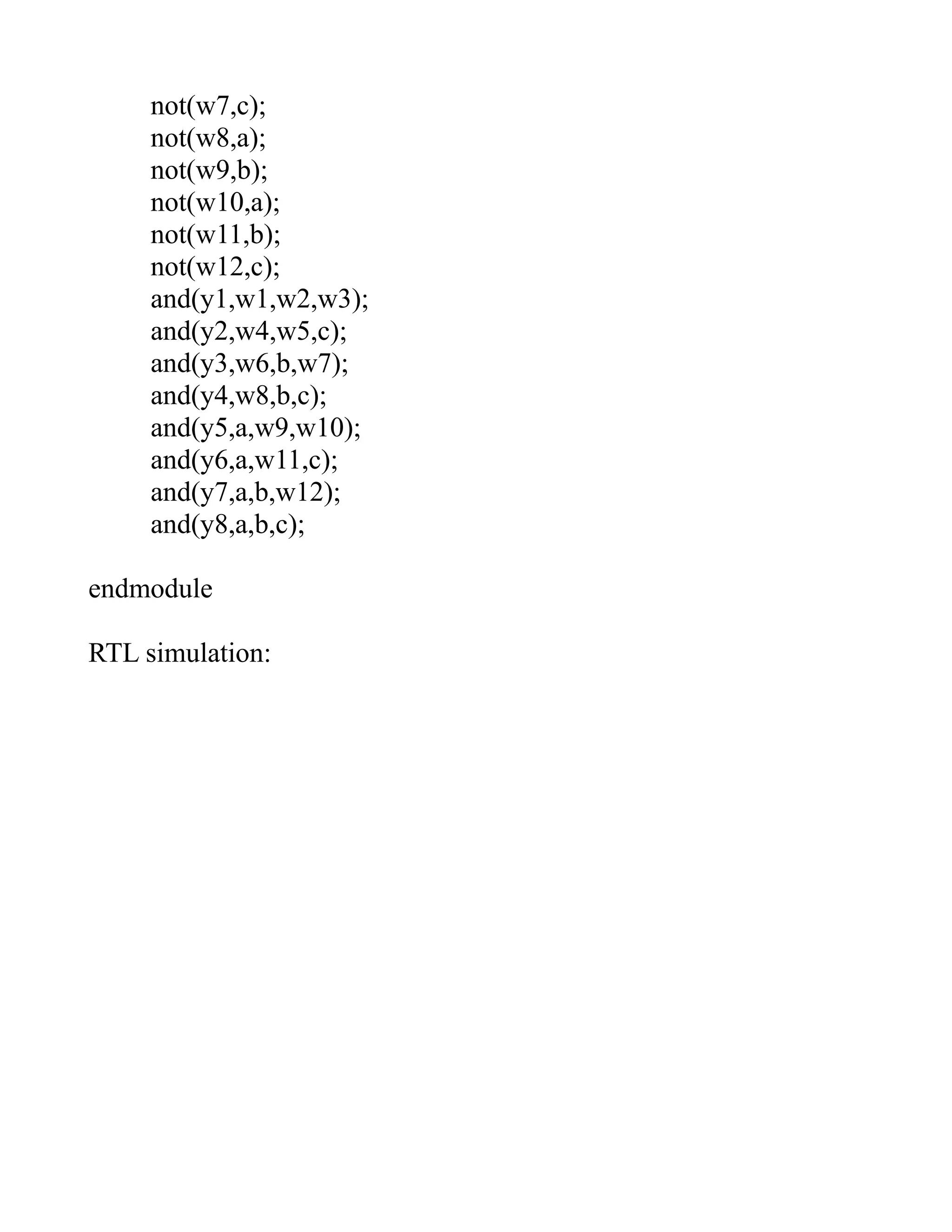

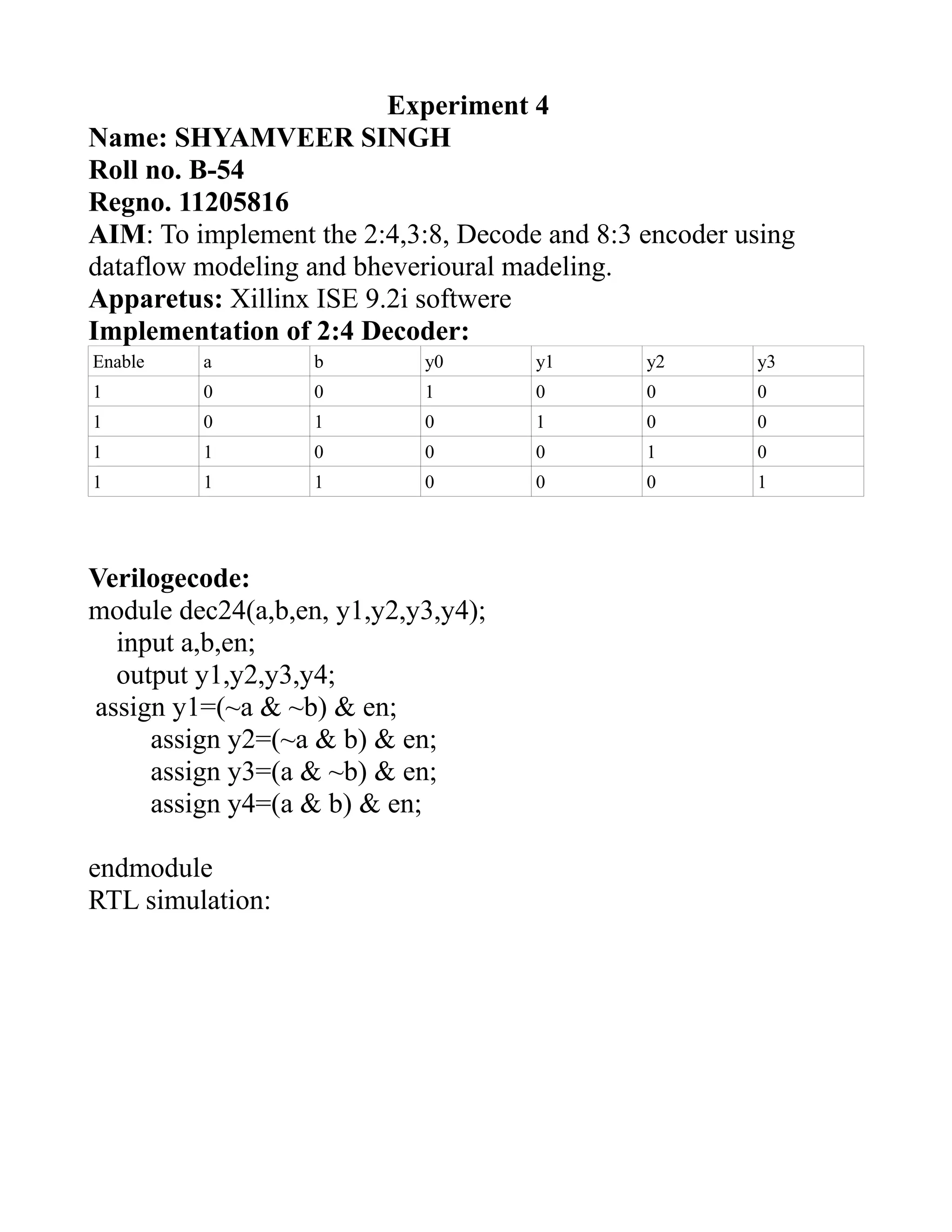

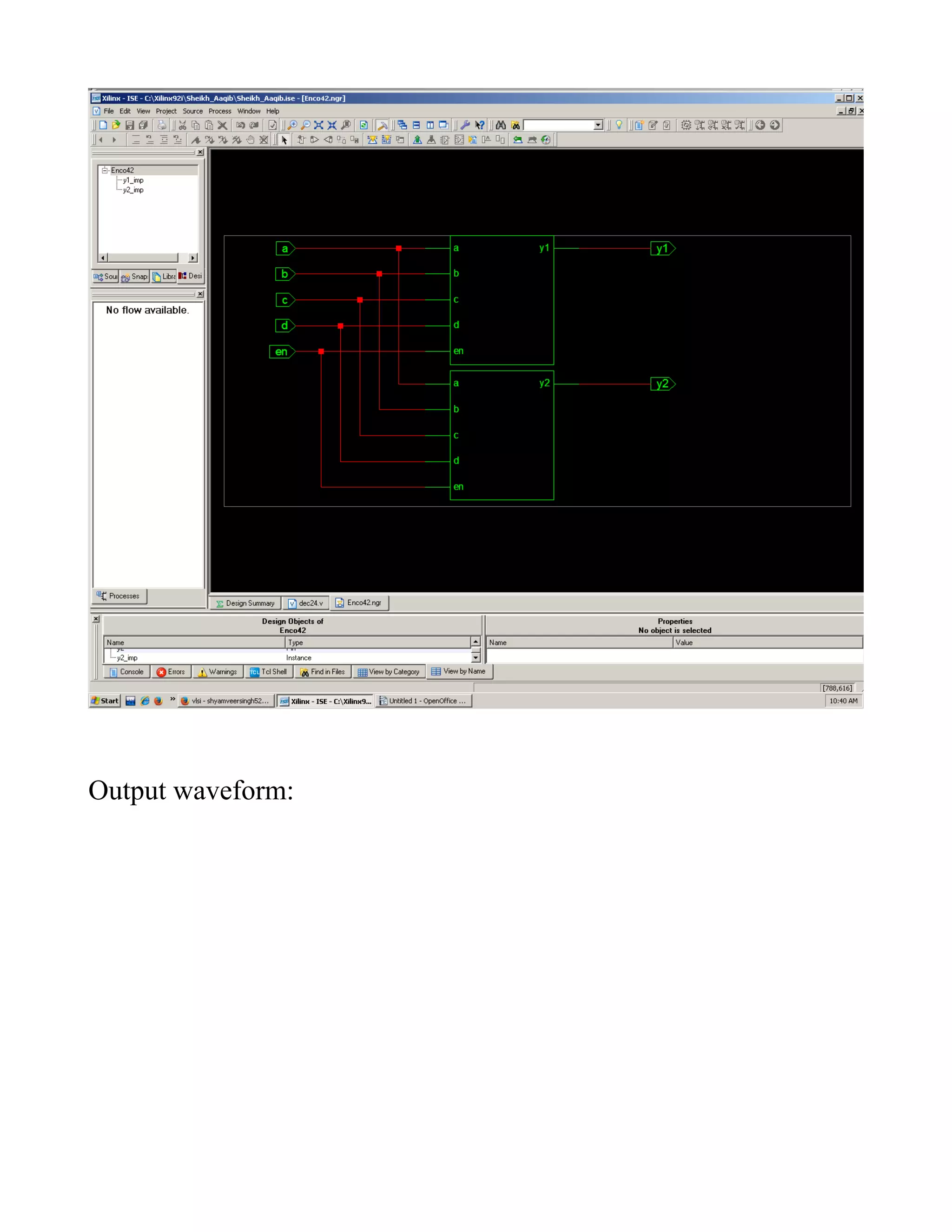

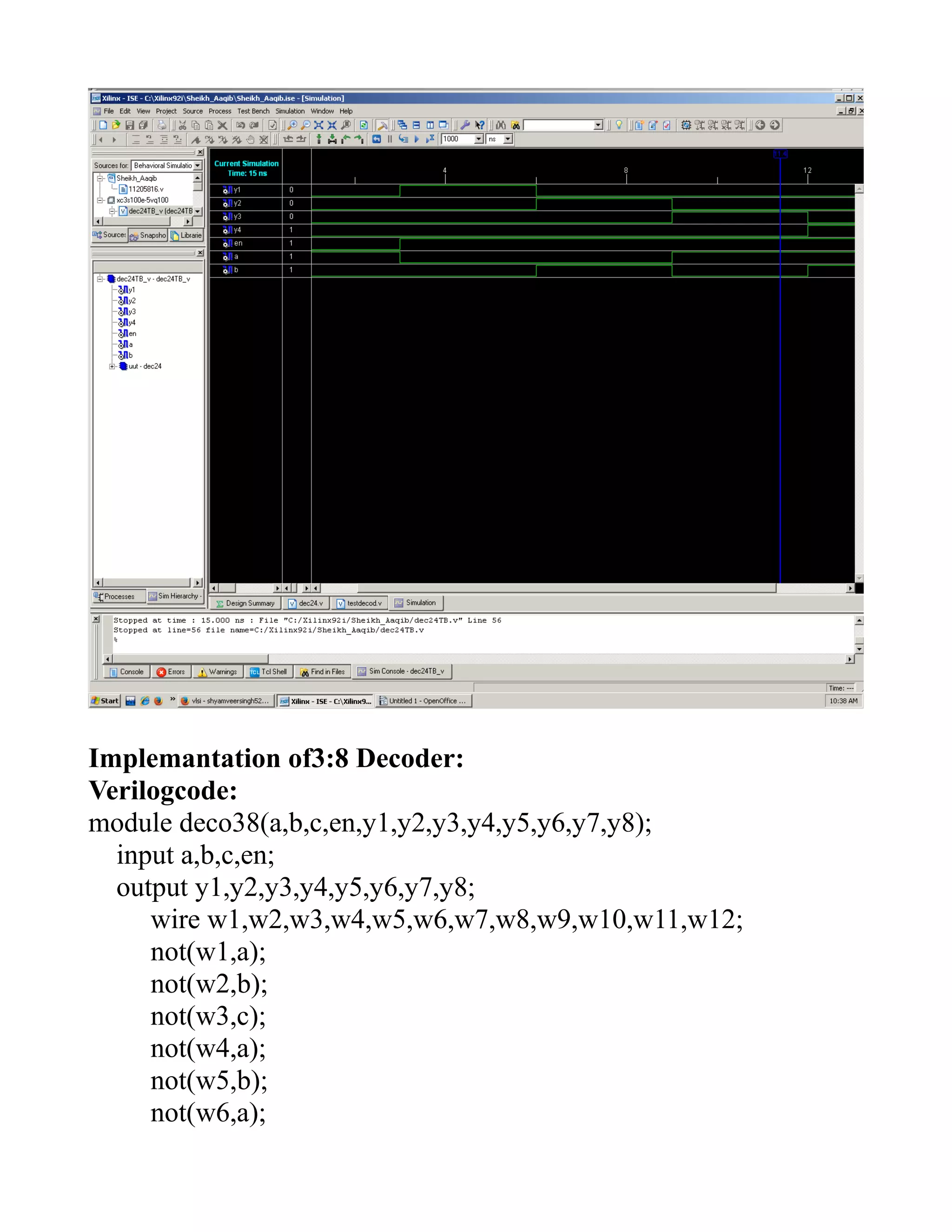

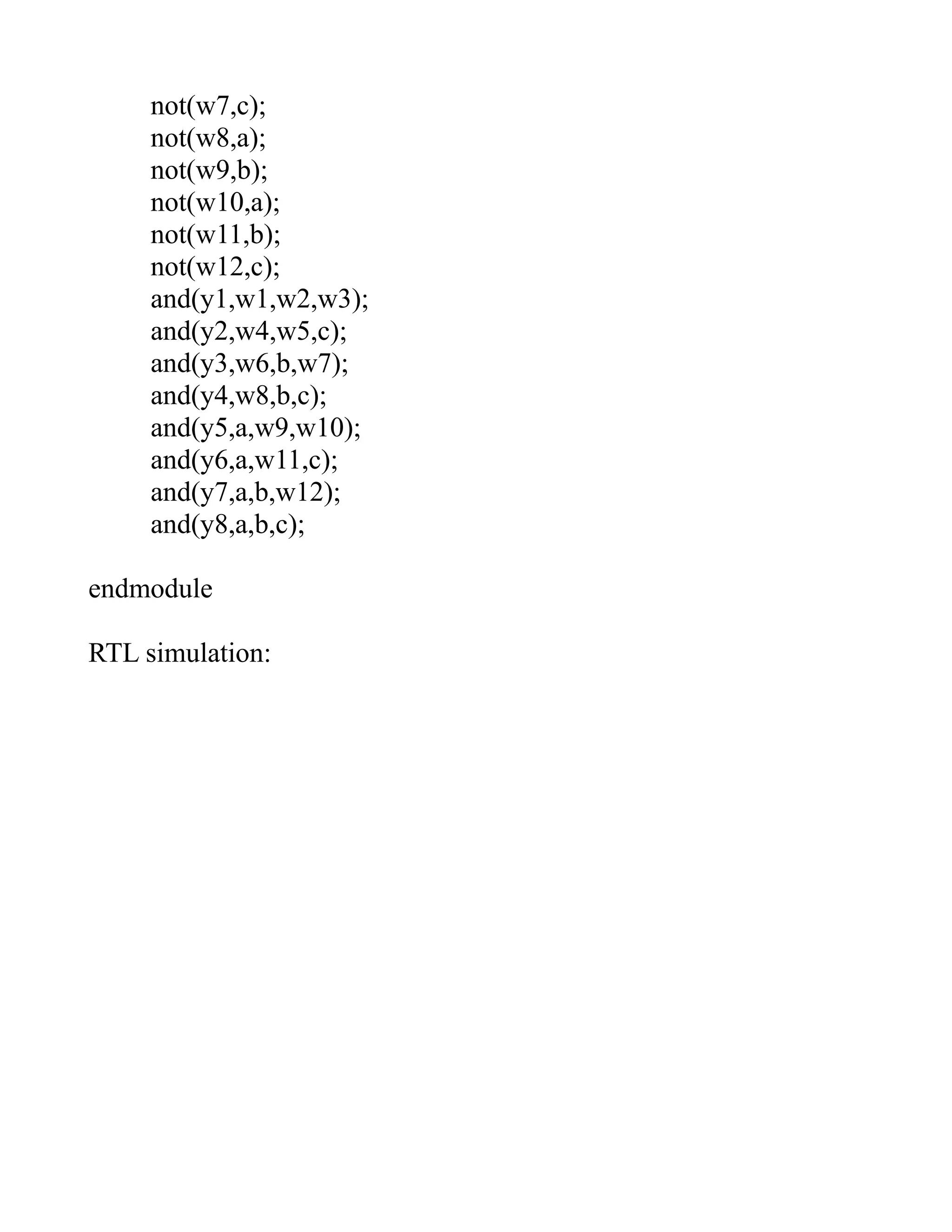

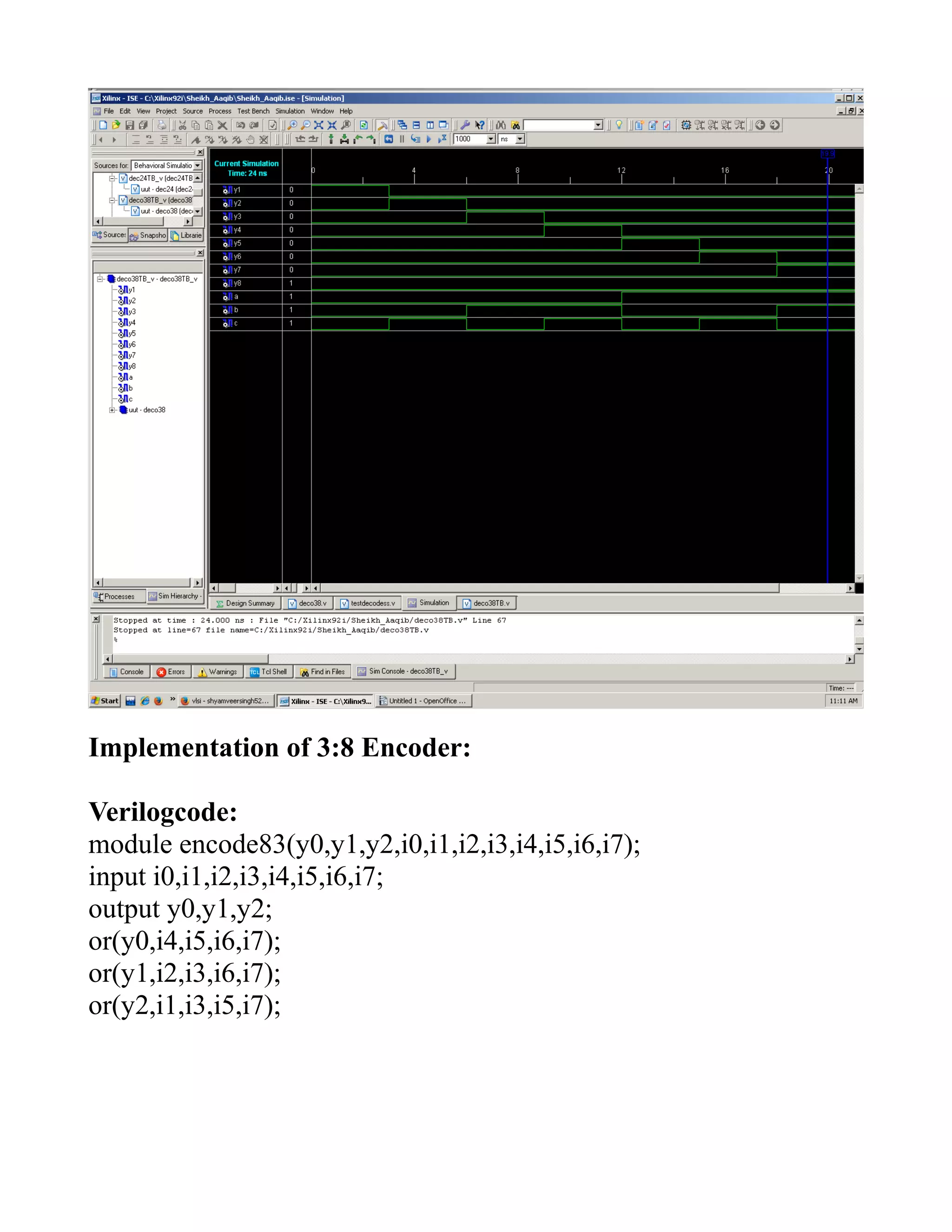

This document summarizes an experiment that implemented 2:4, 3:8 decoders and an 8:3 encoder using Verilog. It provides the Verilog code for each implementation and includes RTL simulation output waveforms. The aim was to model the decoders and encoder using dataflow and behavioral modeling. The experiment was conducted using Xilinx ISE 9.2i software by student SHYAMVEER SINGH with roll number B-54.

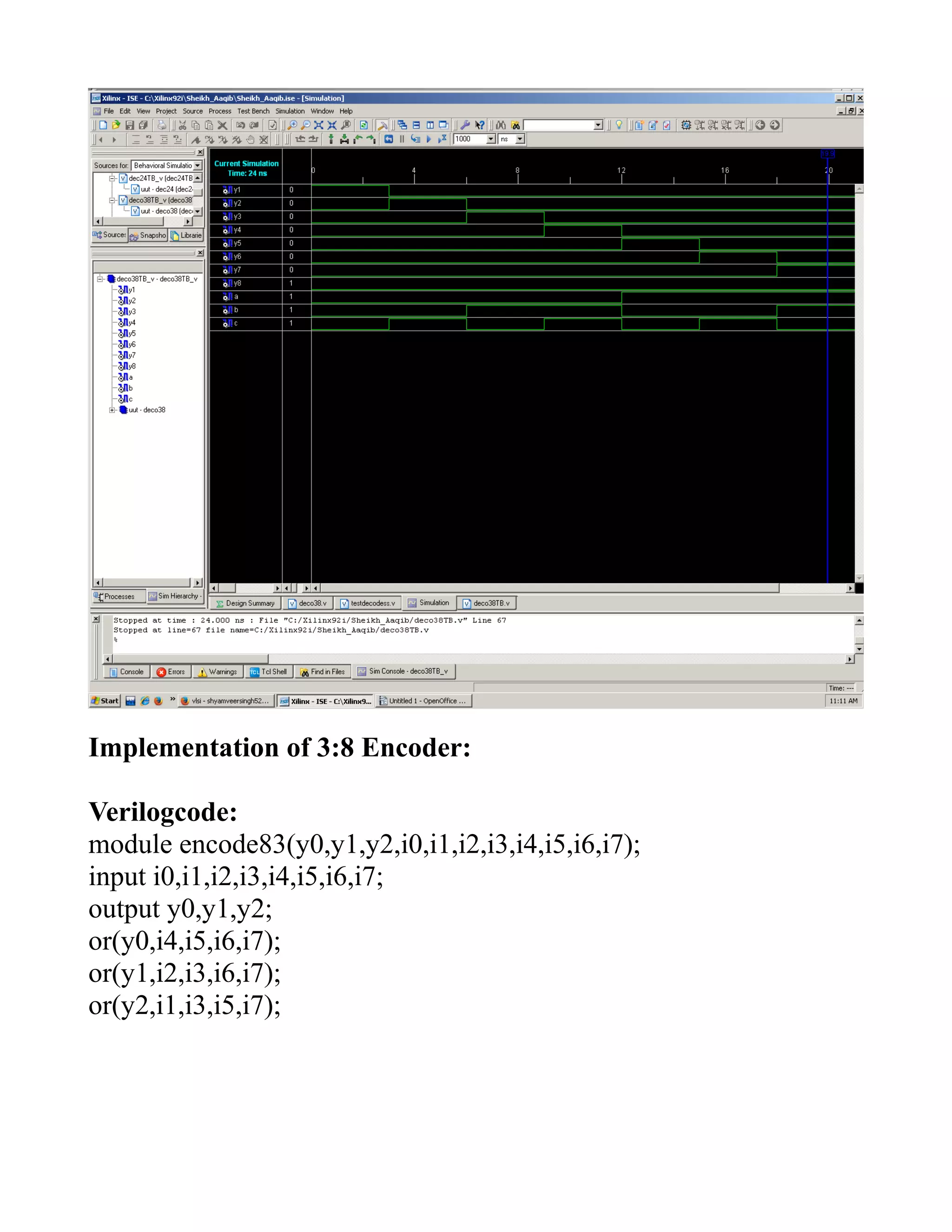

Introduces the 2:4 and 3:8 decoders using Verilog, highlighting their enable signals, truth tables, and RTL simulations.

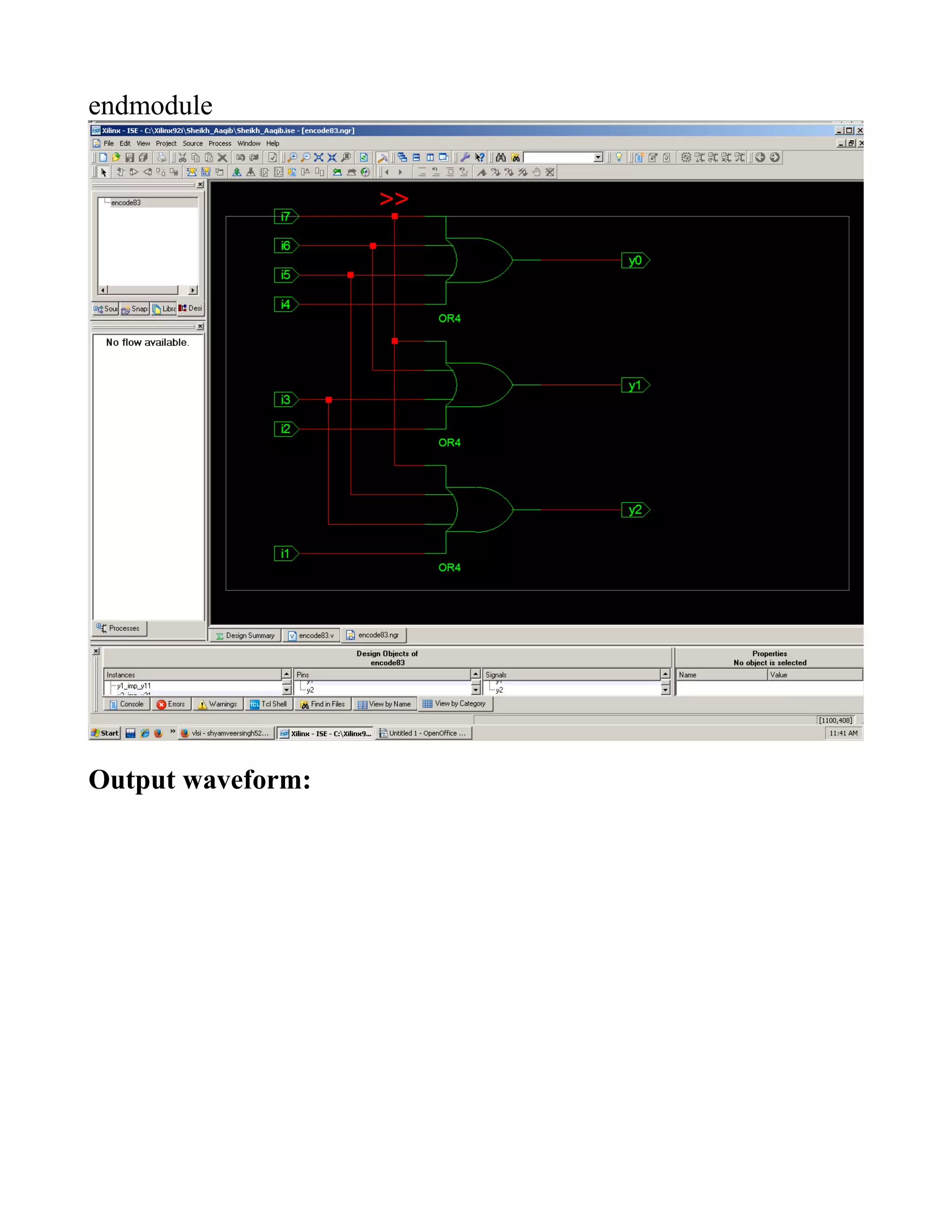

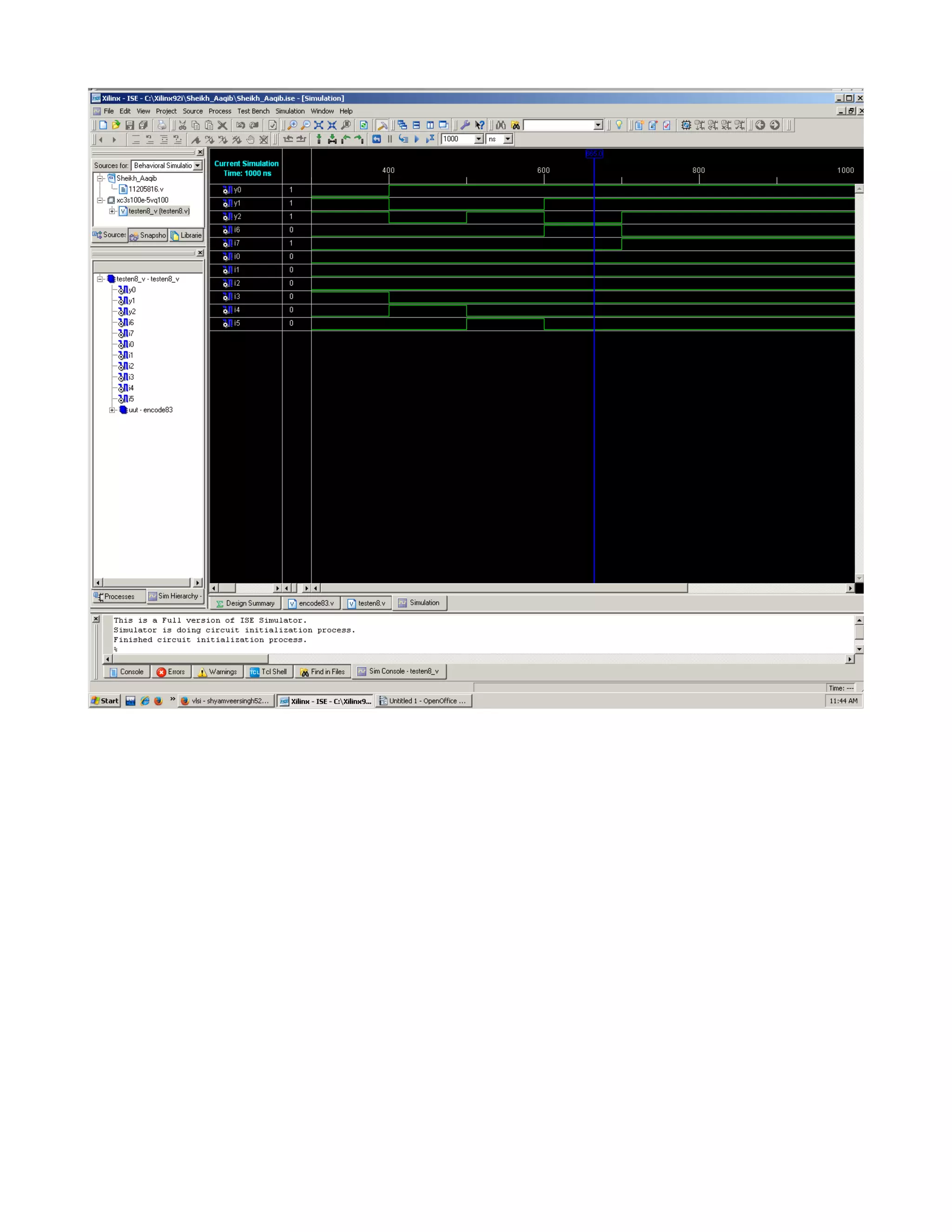

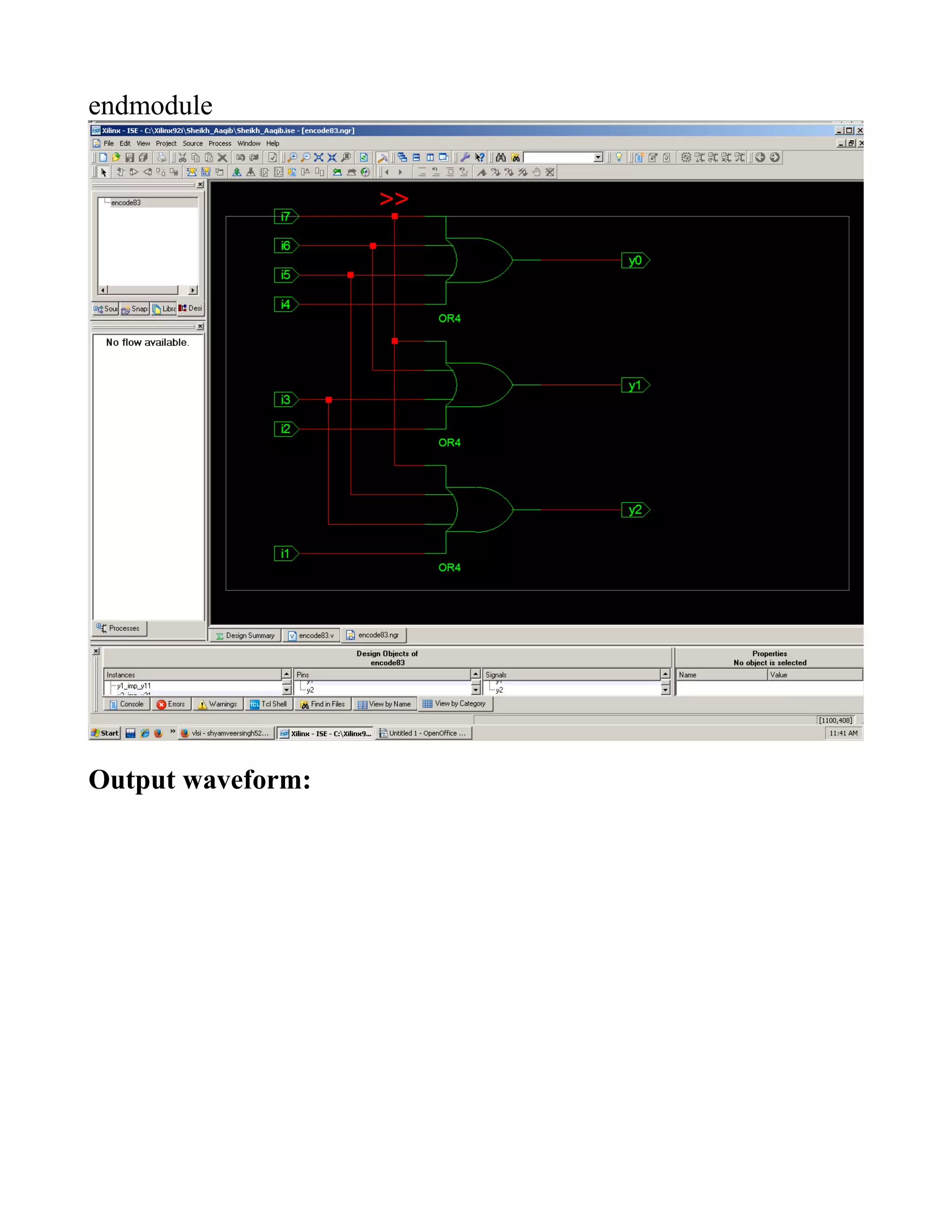

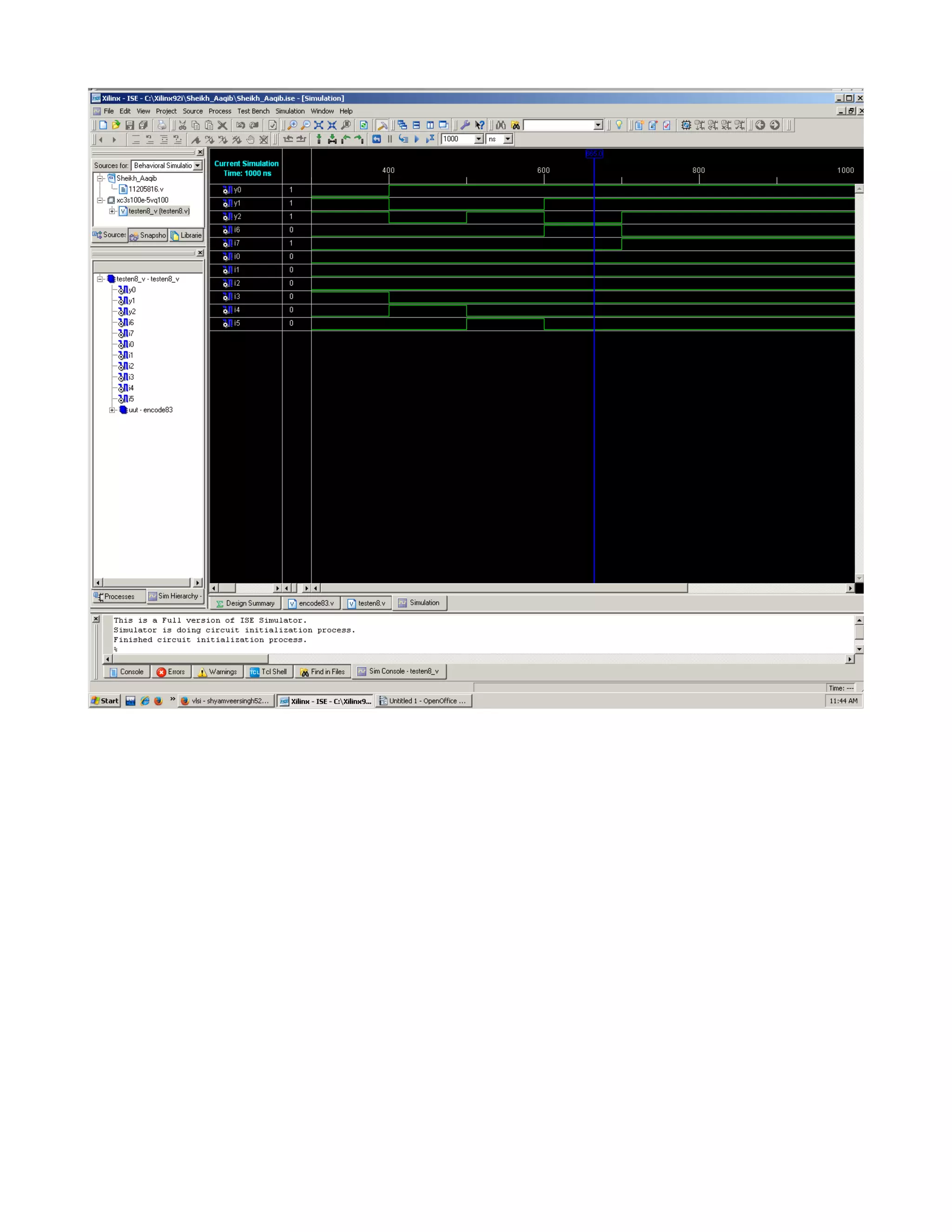

Details the implementation of the 3:8 encoder in Verilog, showcasing input-output relations and output waveforms.