Let's step back a bit and talk about the low level signalling protocol used by UARTs. TX and RX are data lines, not clocks. The clocks are only inside each UART, which is why there has to be agreement up front about what the baud rate is.

When not transmitting the line is left in the idle state. To transmit a byte (for example, other data widths are possible), the transmitter first sends the start bit. The receiver uses the time of the leading edge of the start bit and the known baud rate to then decode the rest of the character. Let's say for simplicity that 100 kBaud is being used. That means each bit time is 10 µs long. This includes the start bit, the data bits, and the stop bit(s). Therefore, the middle of the first data bit will be at 15 µs after the leading edge of the start bit, the second at 25 µs, etc.

As long as the receiver and transmitter clocks are the same, this could go on forever. However, they will never be exactly the same so it can't go on forever. To allow re-synchronization of the receiver's clock to the transmitter's clock, the data character ends, the line is left idle for a bit, then the process is repeated. Timing errors accumulate starting at the leading edge of the start bit, so the maximum drift is at the last bit. Once that character is over, the receiver resets waiting for the next start bit and the process repeats.

With 8 data bits, the worst case for timing is sampling the last bit. That is 8.5 bit times from the timing reference, which is the leading edge of the start bit. If the receiver is off by 1/2 bit or more then, it will sample the last bit during a different bit. Clearly that is bad. This happens at a clock frequency mismatch of 1/2 bit in 8 1/2 bits, or 5.9%. That's the guaranteed to fail mismatch. For reliability, you usually want to make sure the receiver matches the transmitter to within half of that, or 2.9%. That represents a 1/4 bit time error at the last bit.

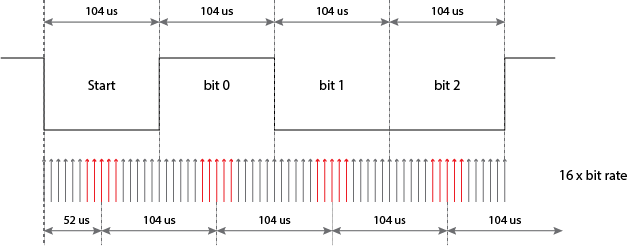

However, it's not quite that simple. In the scenario described above, the receiver essentially starts a stopwatch at the leading edge of the start bit. That could in theory be done in analog electronics, but that would be complicated and expensive and not easily integratable onto digital chips. Instead, most digital UART implementations have a internal clock that runs at 16x the expected bit rate. The "stopwatch" then counts these 16x cycles. That means there is a additional possible error of 1/16 bit added to all bit sampling times, which is like another .7% clock mismatch at the last bit.

Hopefully this makes it clear what the stop bit is, how bit timing works, and what the 16x clock is all about. I mostly skipped over stop bits, but maybe you can see for yourself now why at least one stop bit is required. Basically the stop bits are the minimum enforced line idle time between characters. This is the time during which the receiver has finished receiving a character and is ready for the next leading edge of a start bit. If there was no stop bit, then the last data bit could be the same polarity as the start bit and the receiver would have no edge to start its stopwatch on.

Long ago this protocol was decoded by cams, levers, and spinning wheels. Two stop bits were often used to allow the mechanism to reset. Nowadays, everything is done in digital logic and 1 stop bit is used pretty much universally. You often see the low level protocol written shorthand as 8-N-1, meaning 8 data bits, no parity bits (forget about these, they are rarely used today), and 1 stop bit. The start bit is implied since there is no option there.

Using 8-N-1, a 8 bit byte of data actually takes 10 bit times to send. This is one reason there is a distinction between "bit rate" and "baud rate". Baud rate refers to the individual bit signalling times, including the start and stop bits. At 100 kBaud, each bit that is transmitted takes 10 µs, including the start and stop bits. The whole character therefore takes 100 µs, but only 8 bits of real data are transferred. The baud rate is 100 k, but the data transfer bit rate from the point of view of higher levels is only 80 kBits/s.