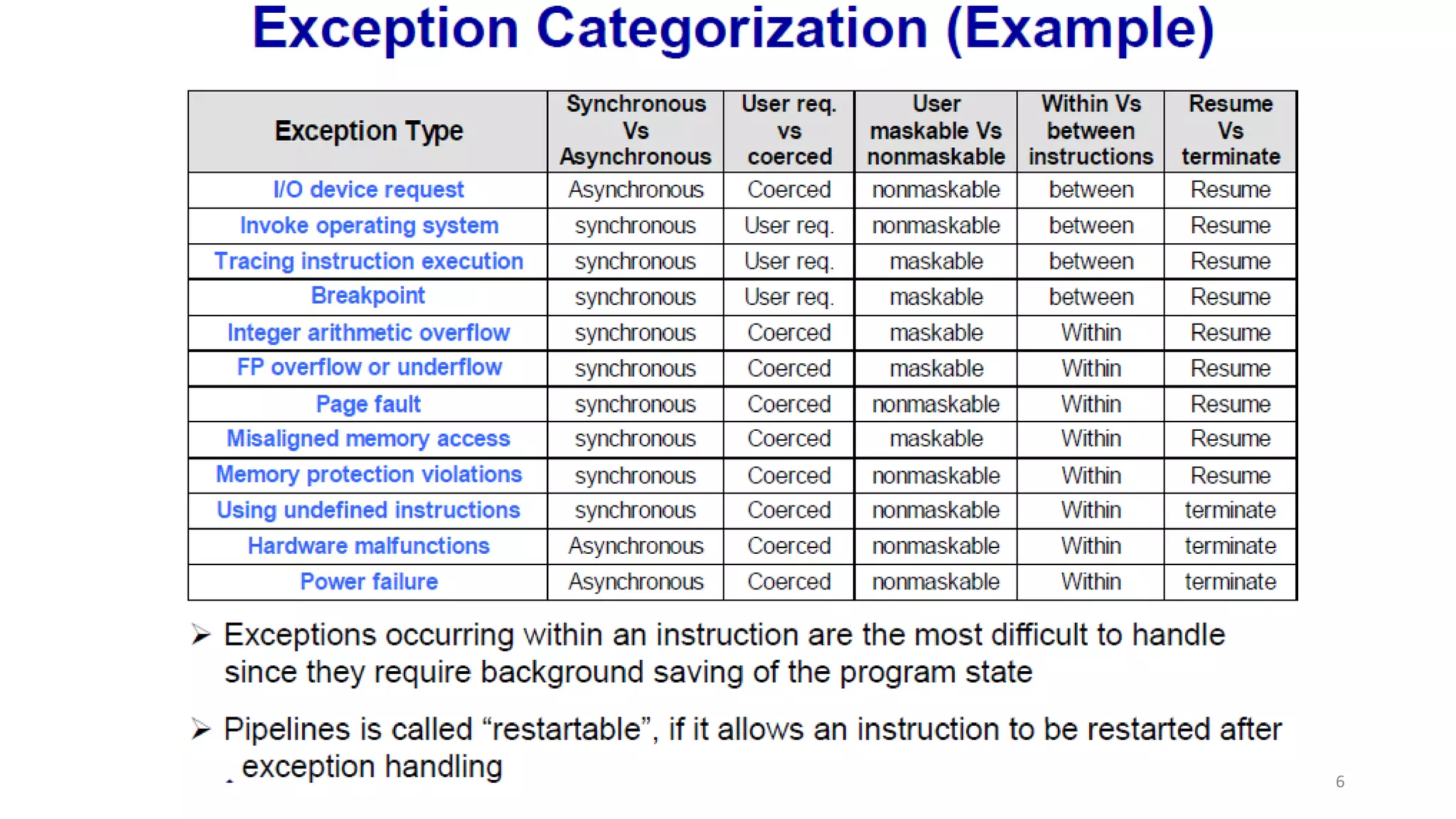

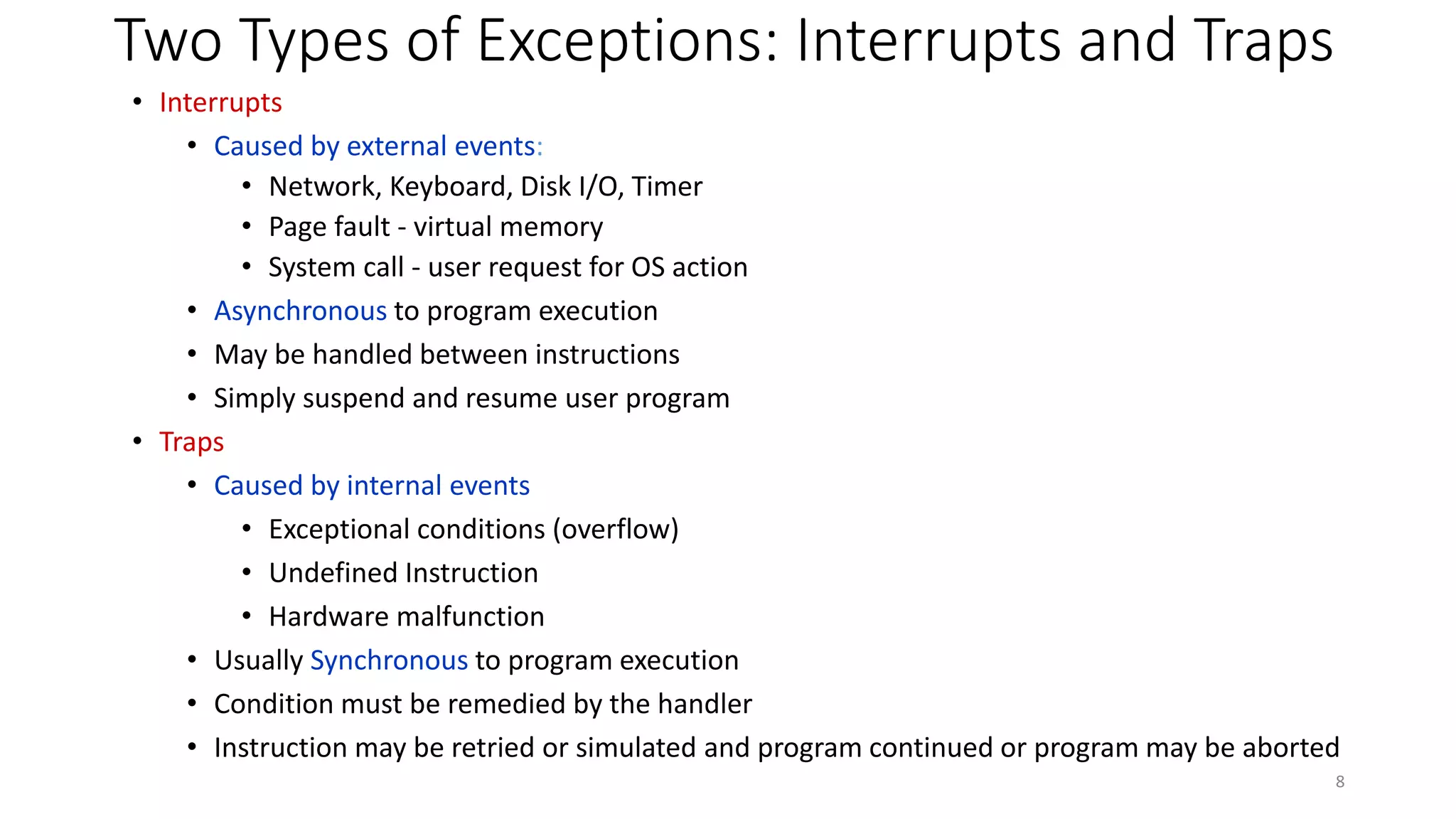

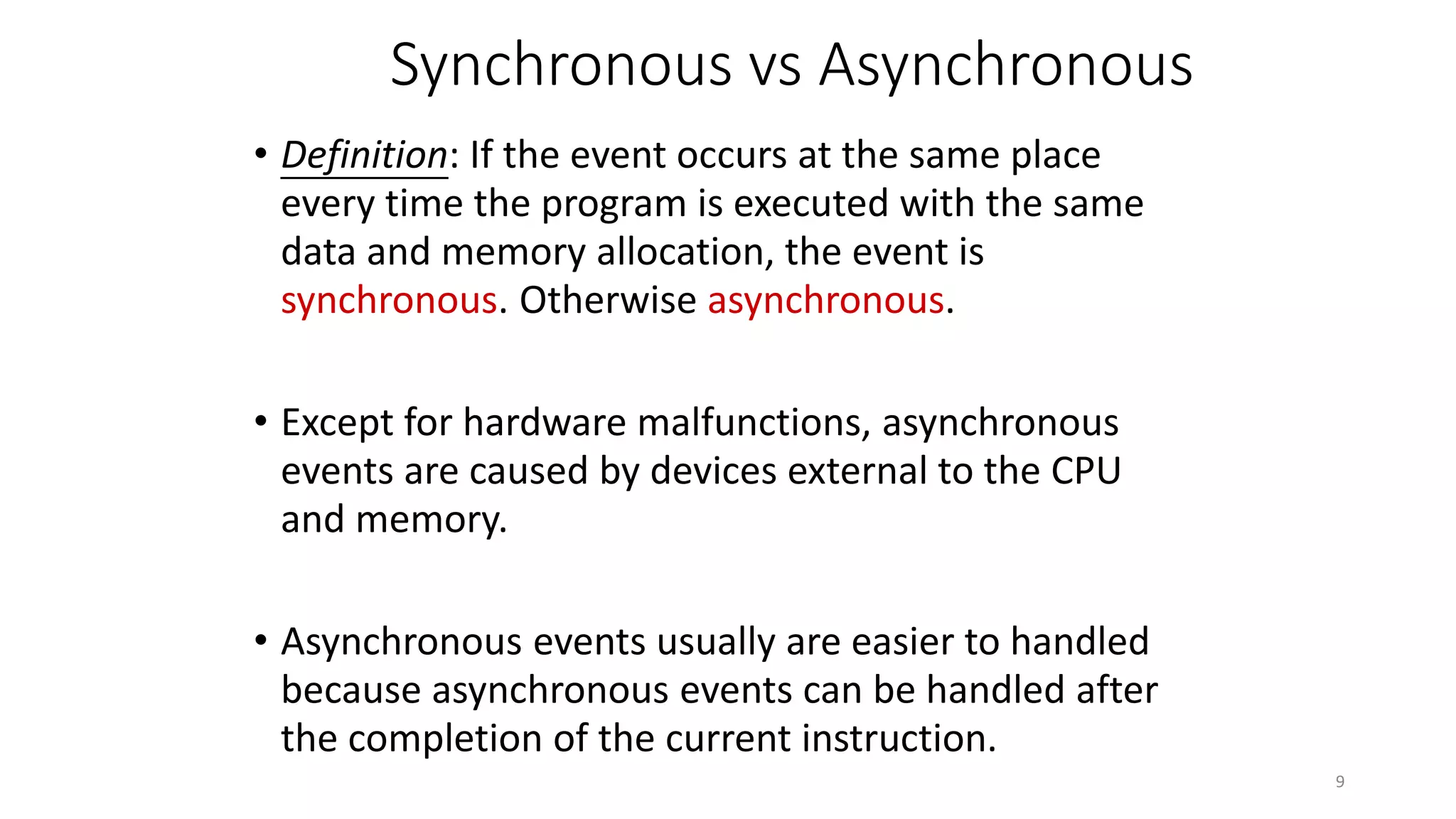

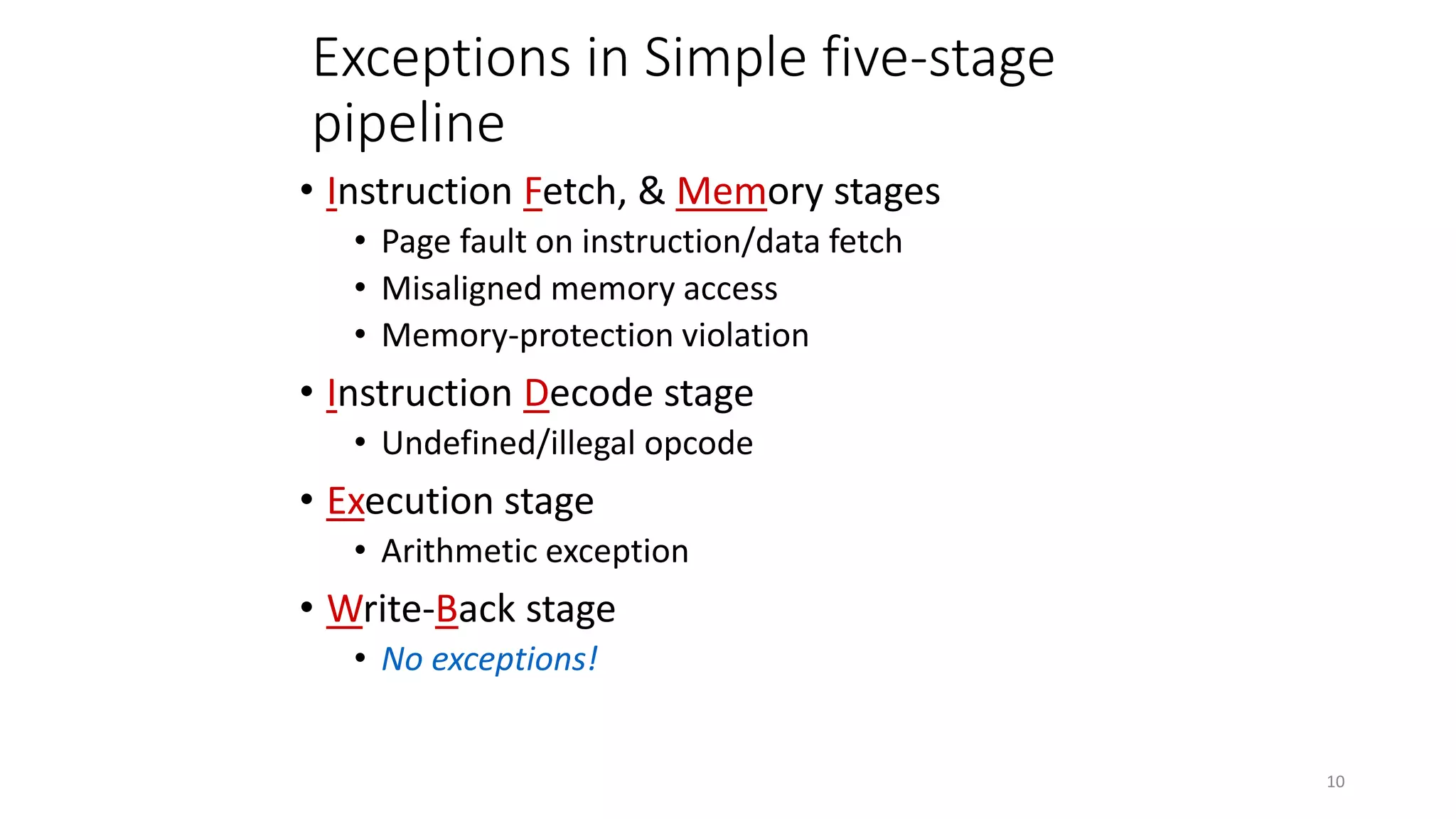

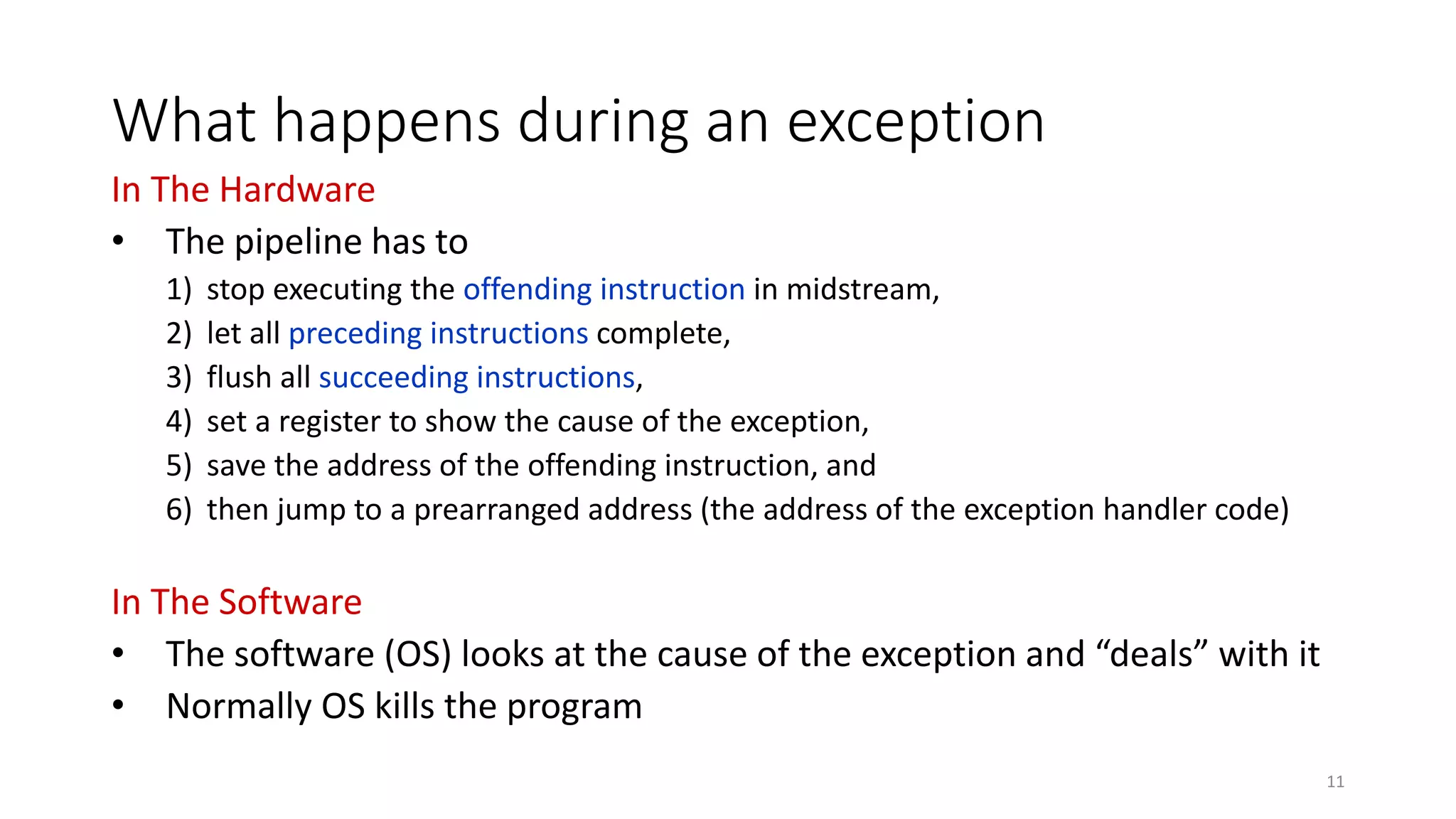

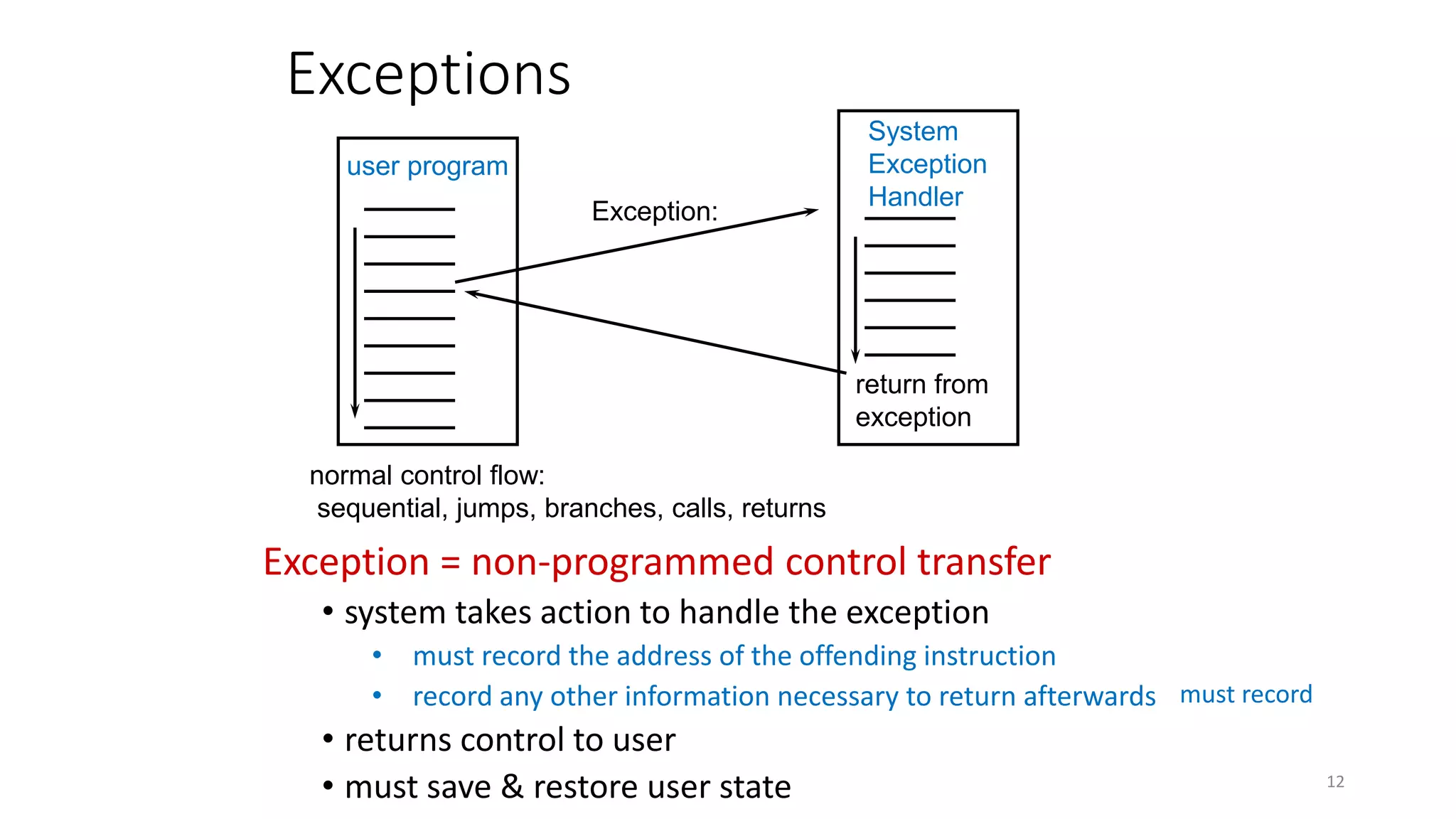

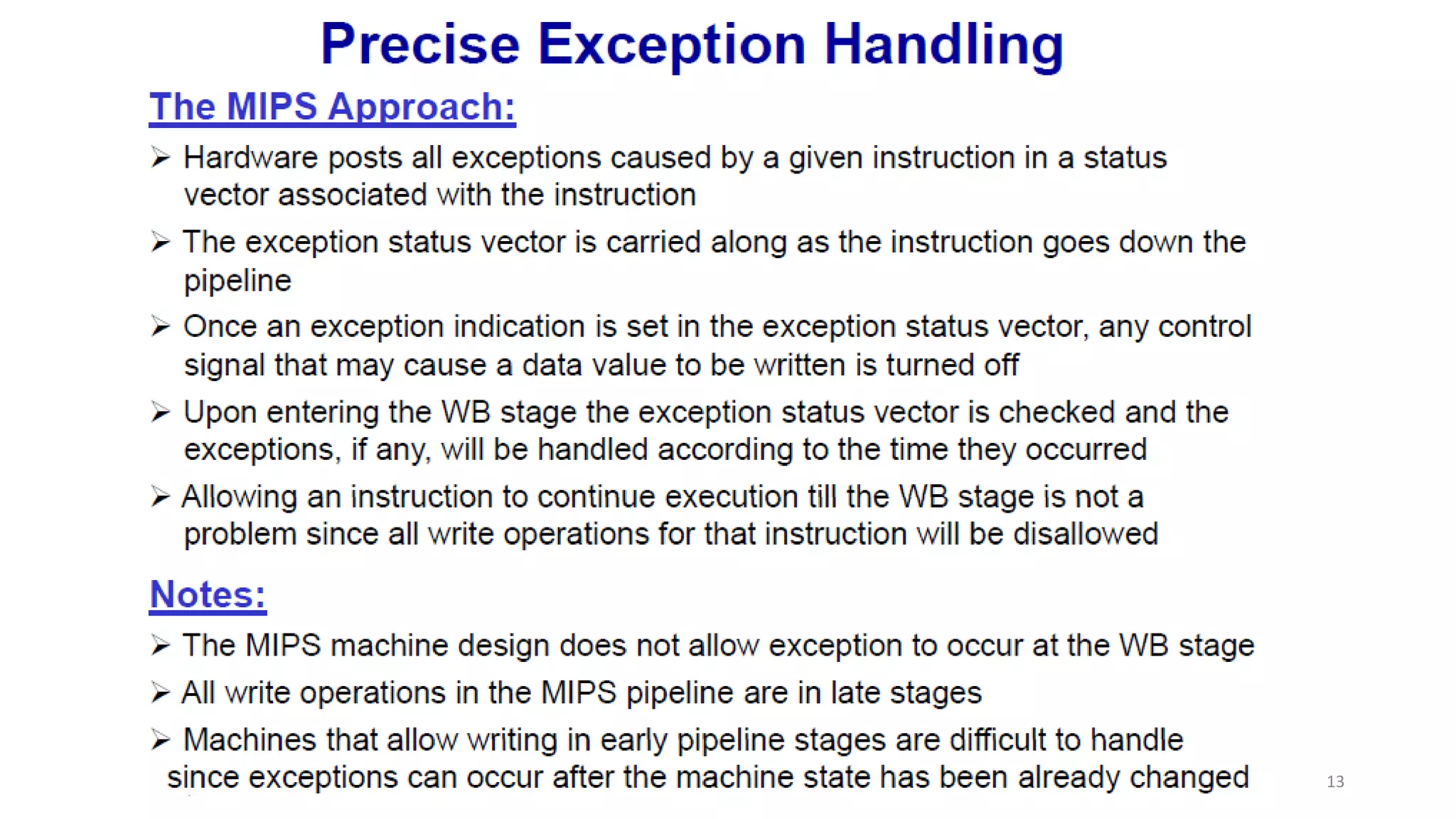

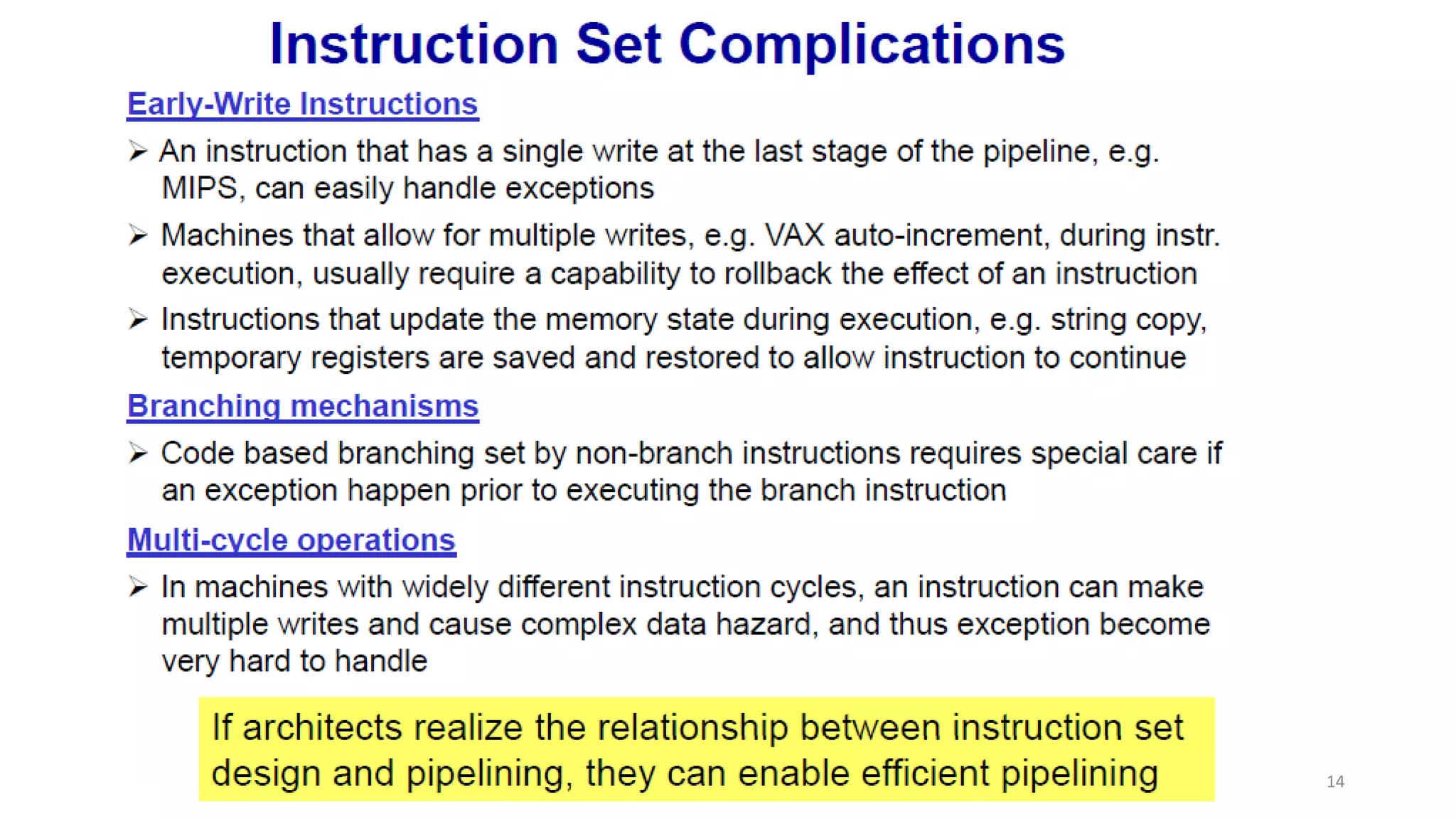

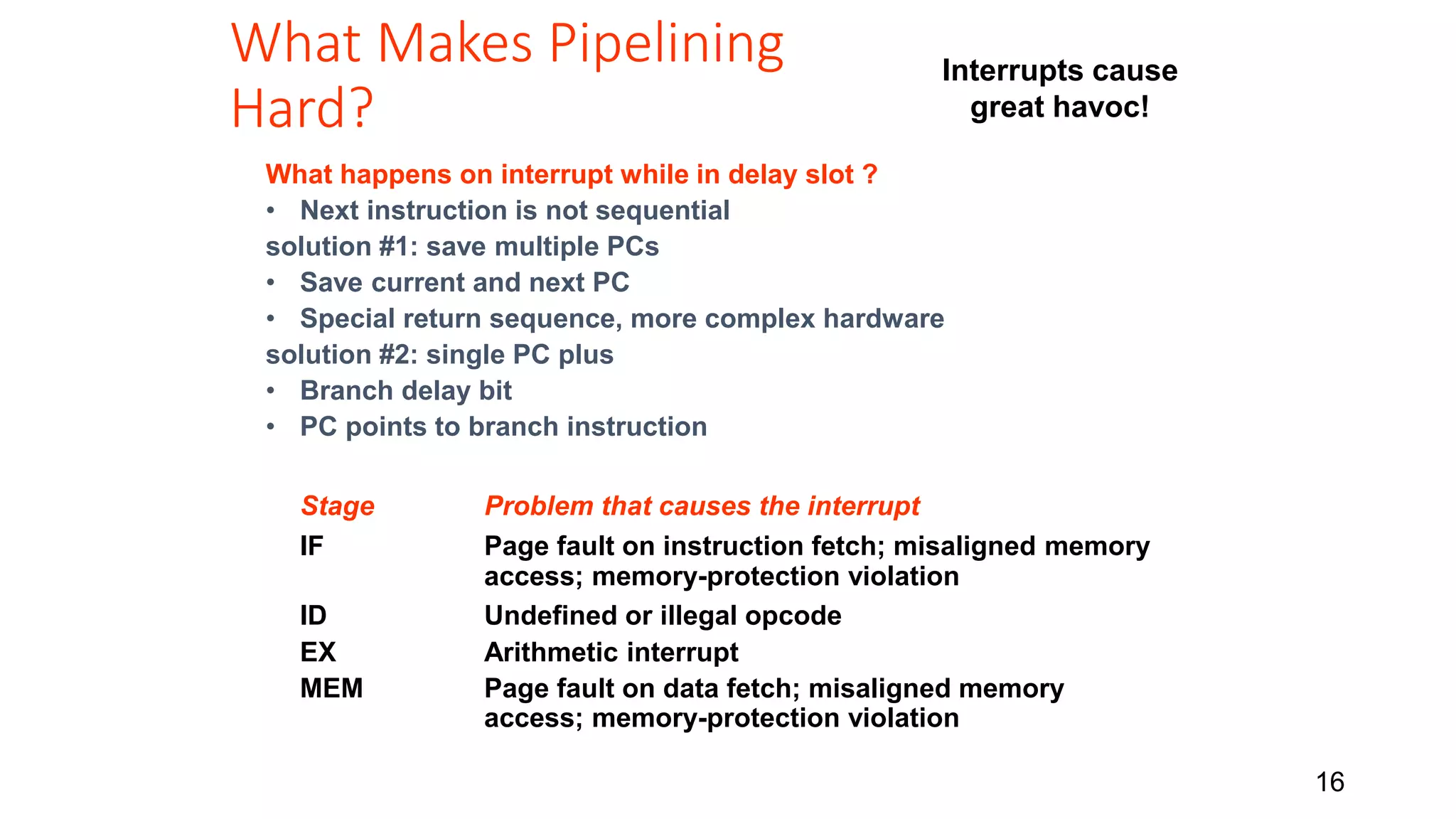

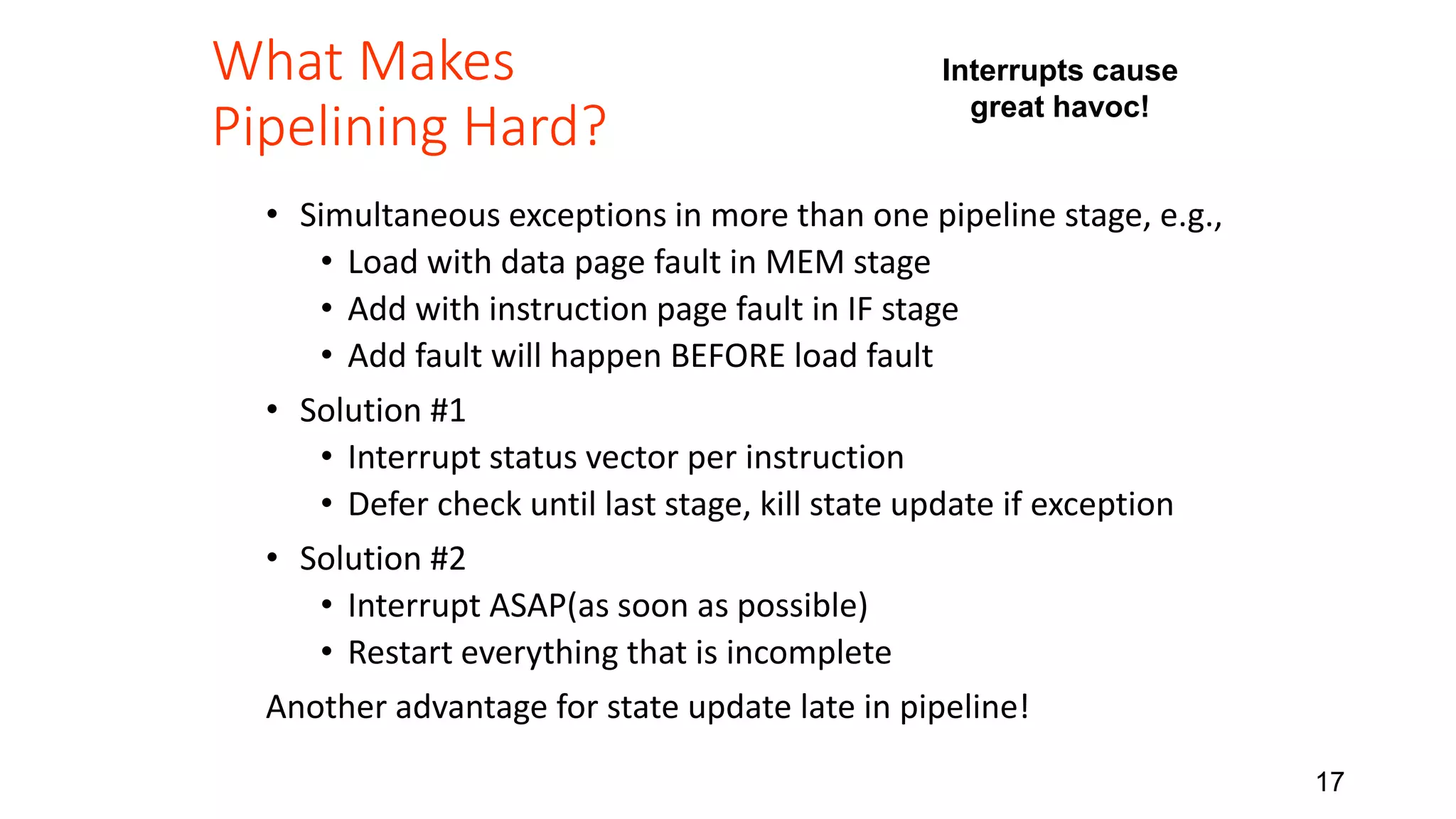

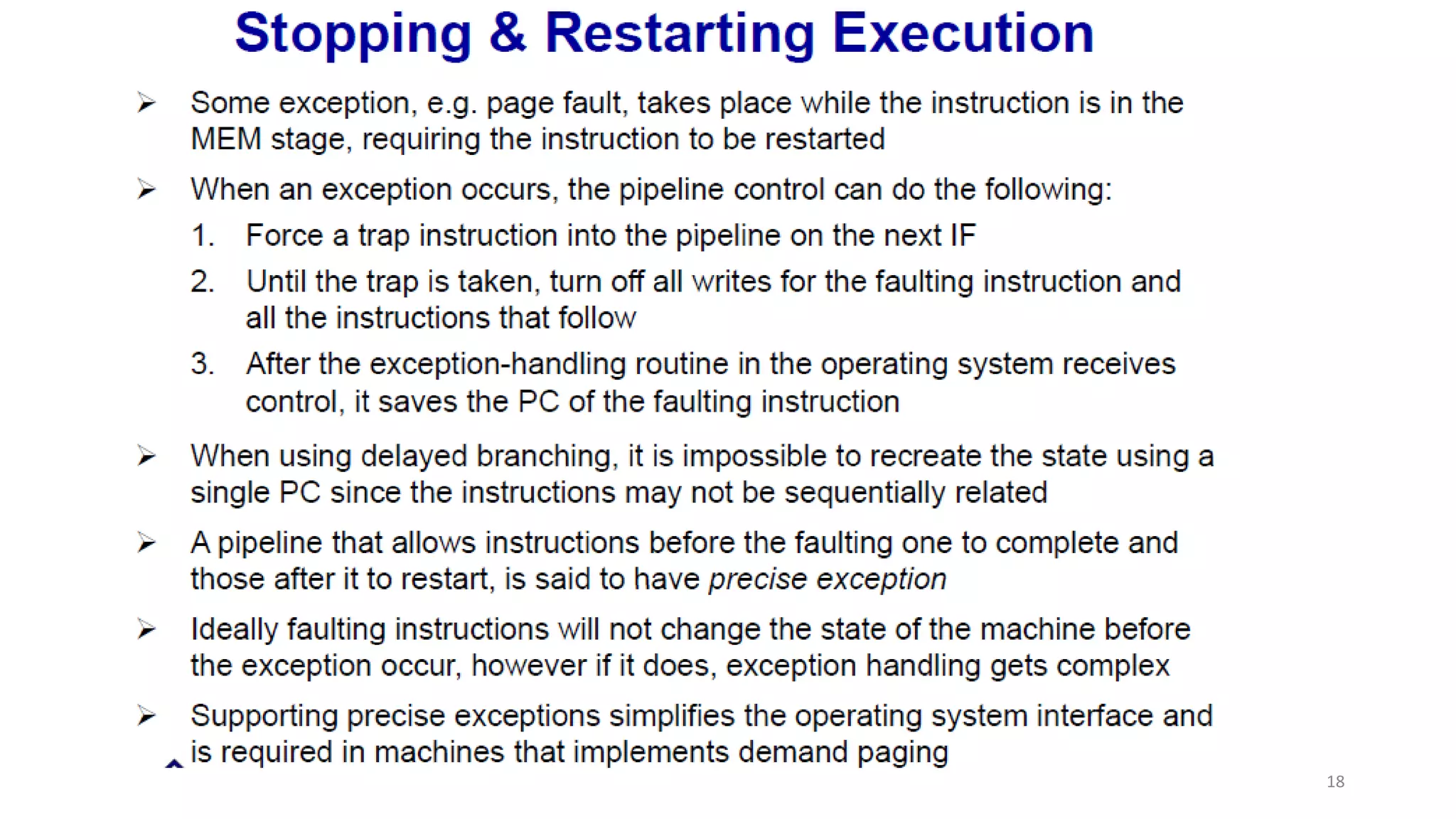

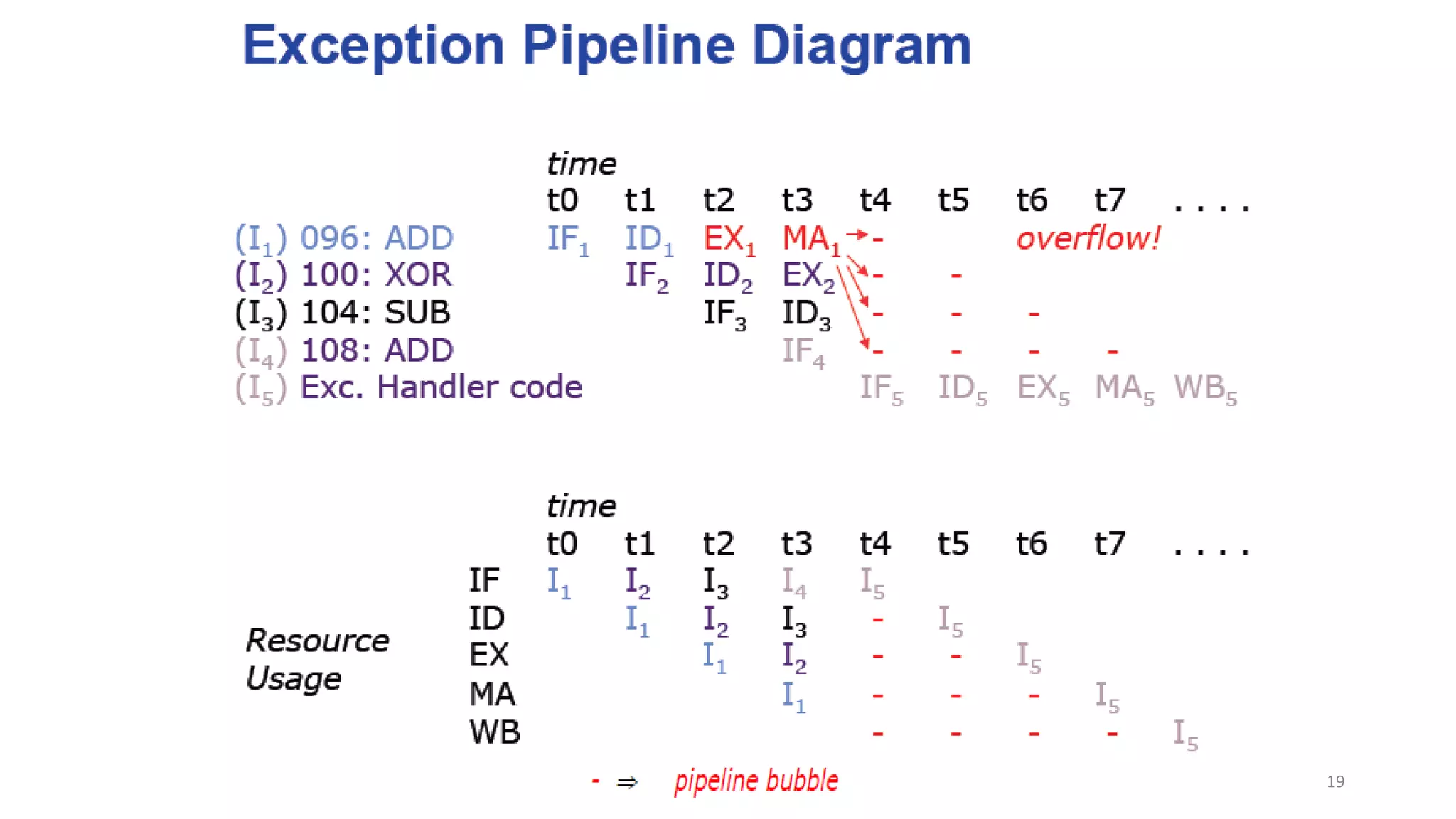

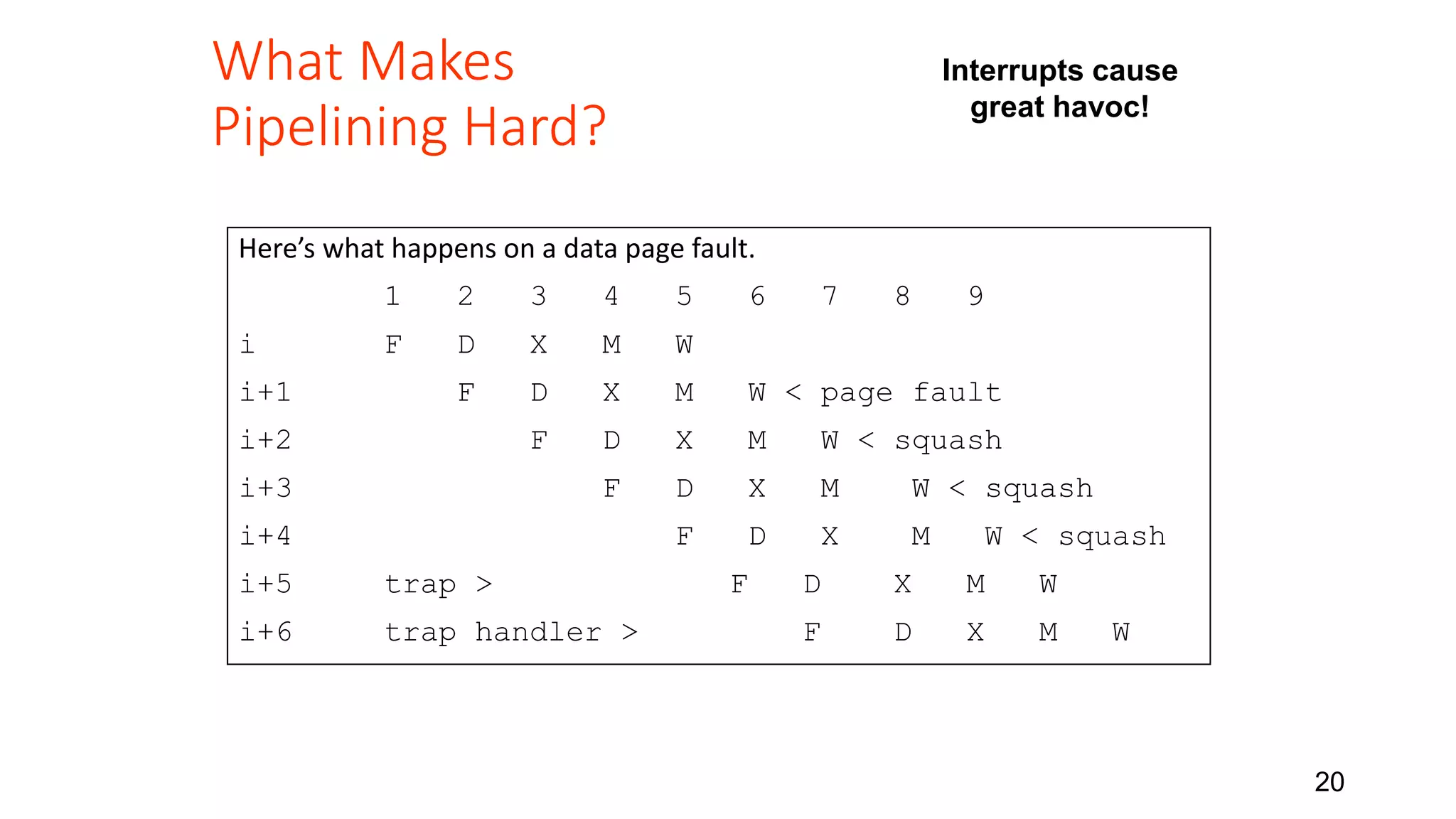

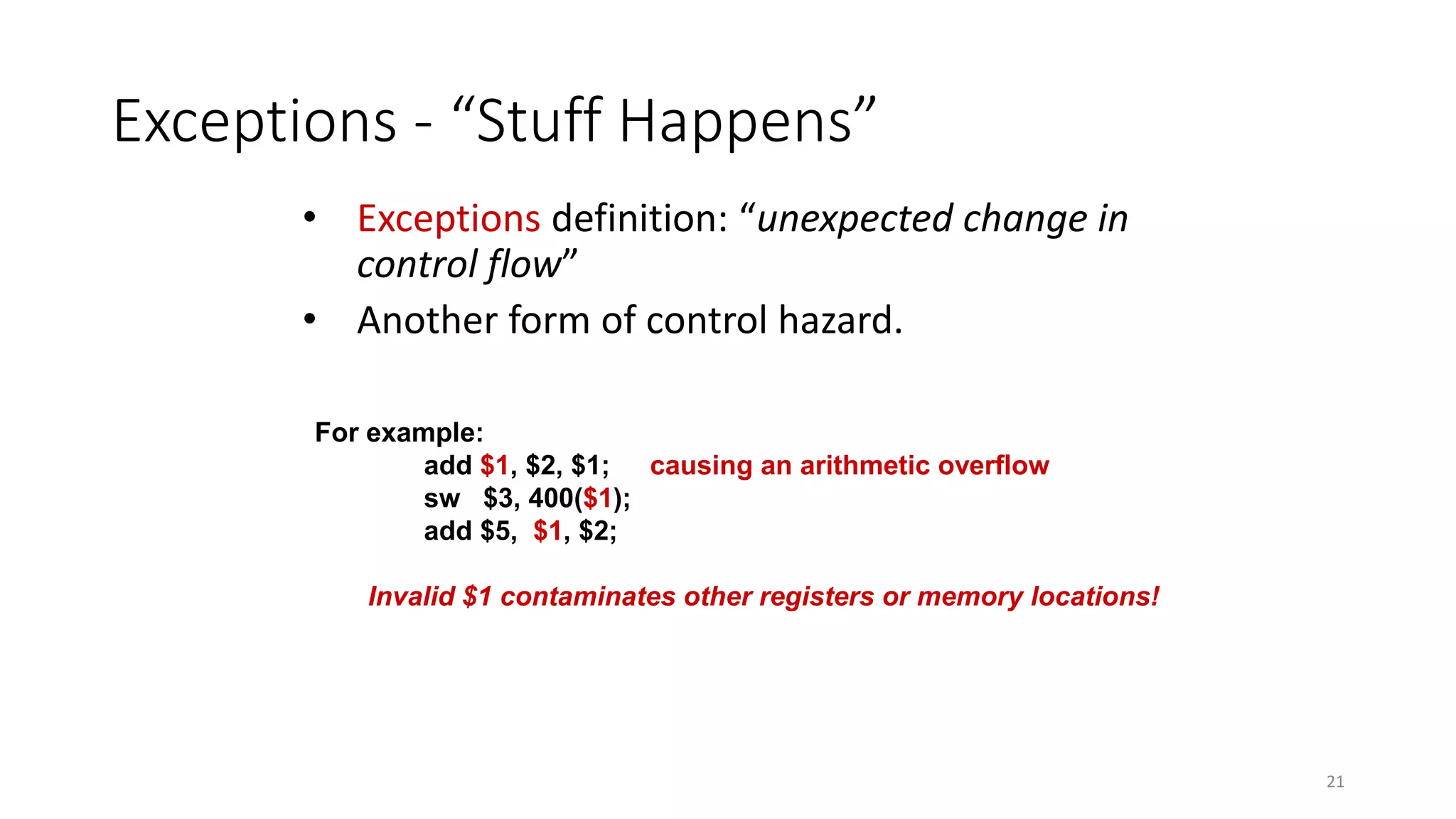

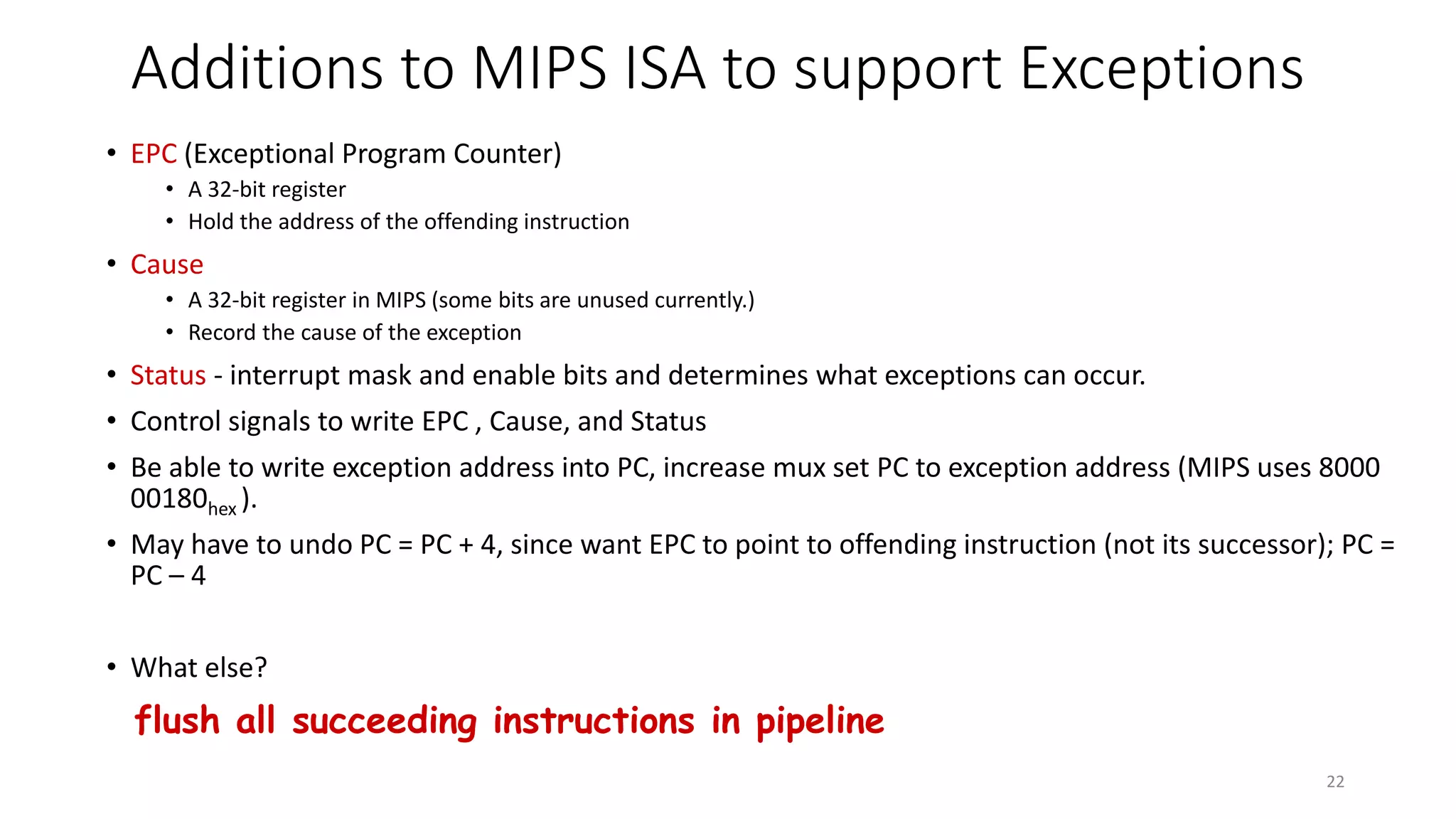

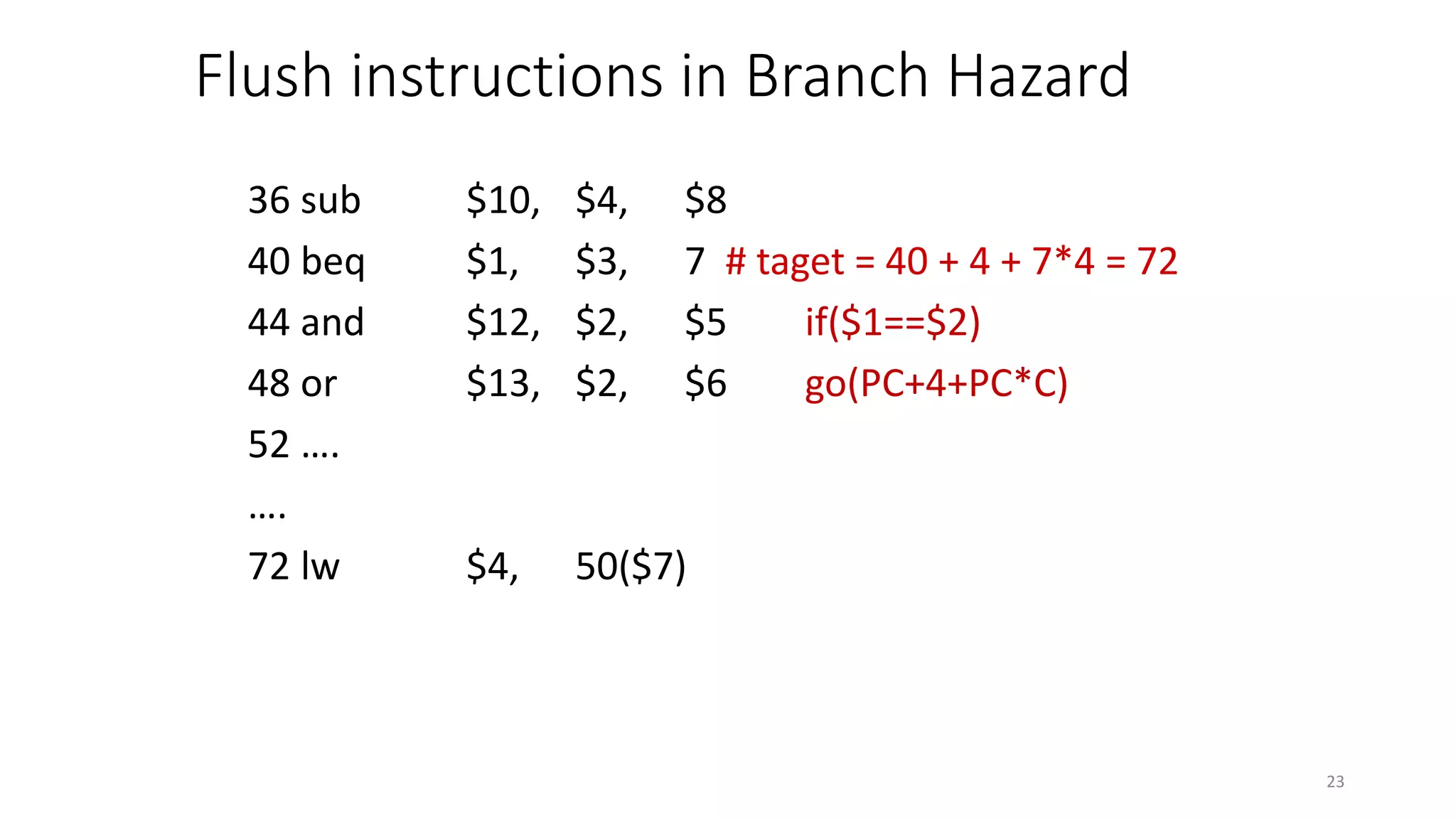

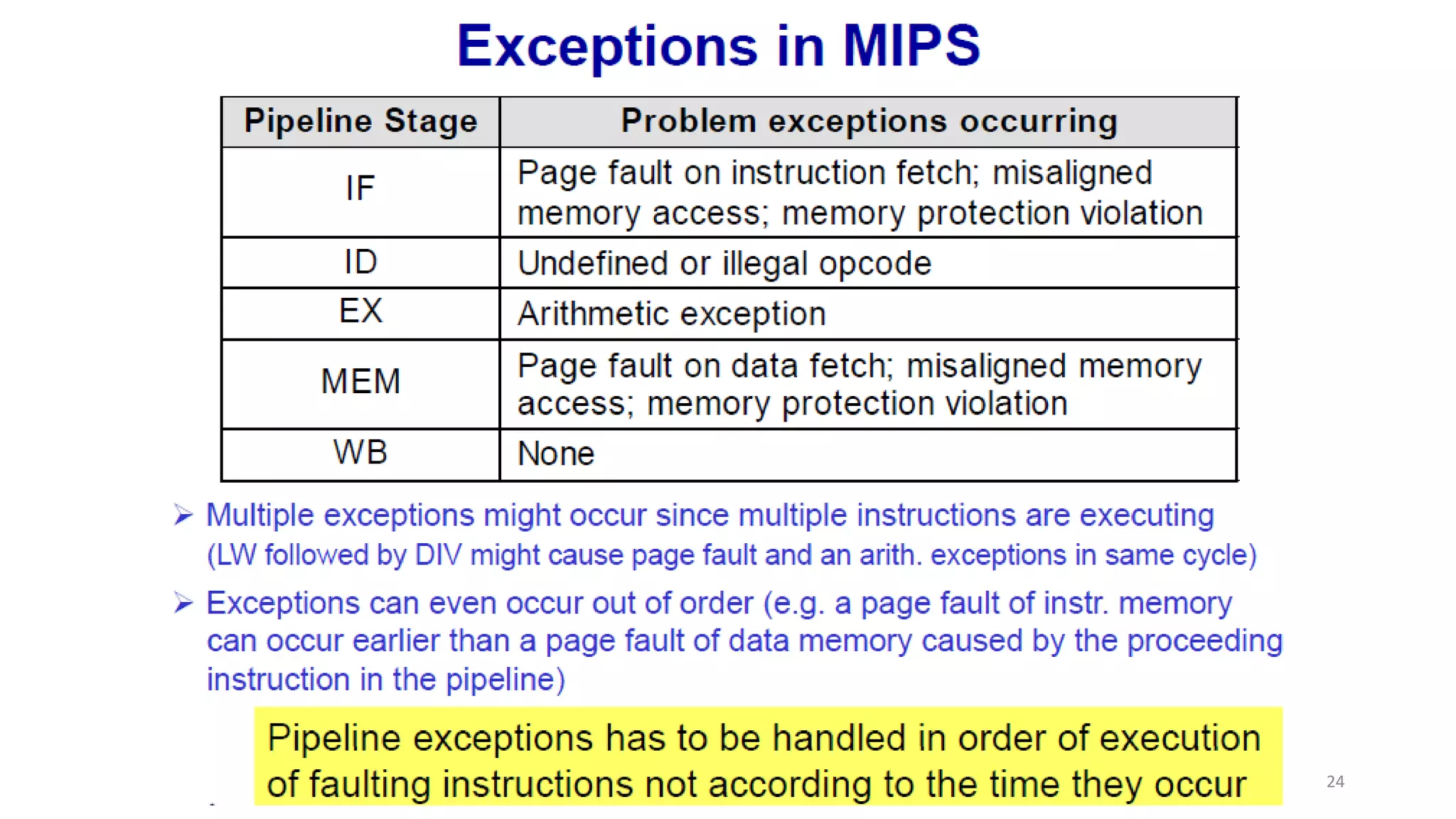

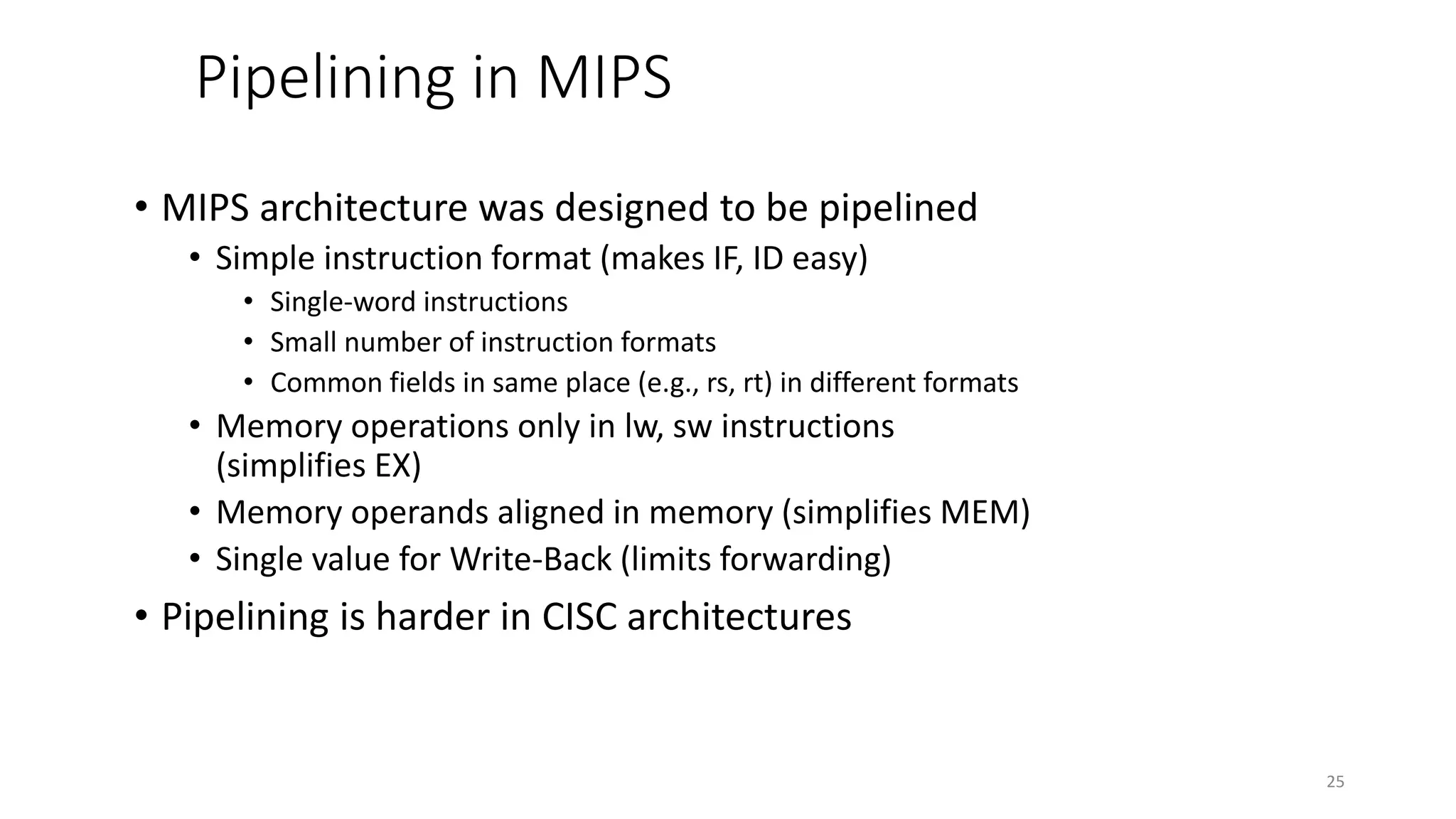

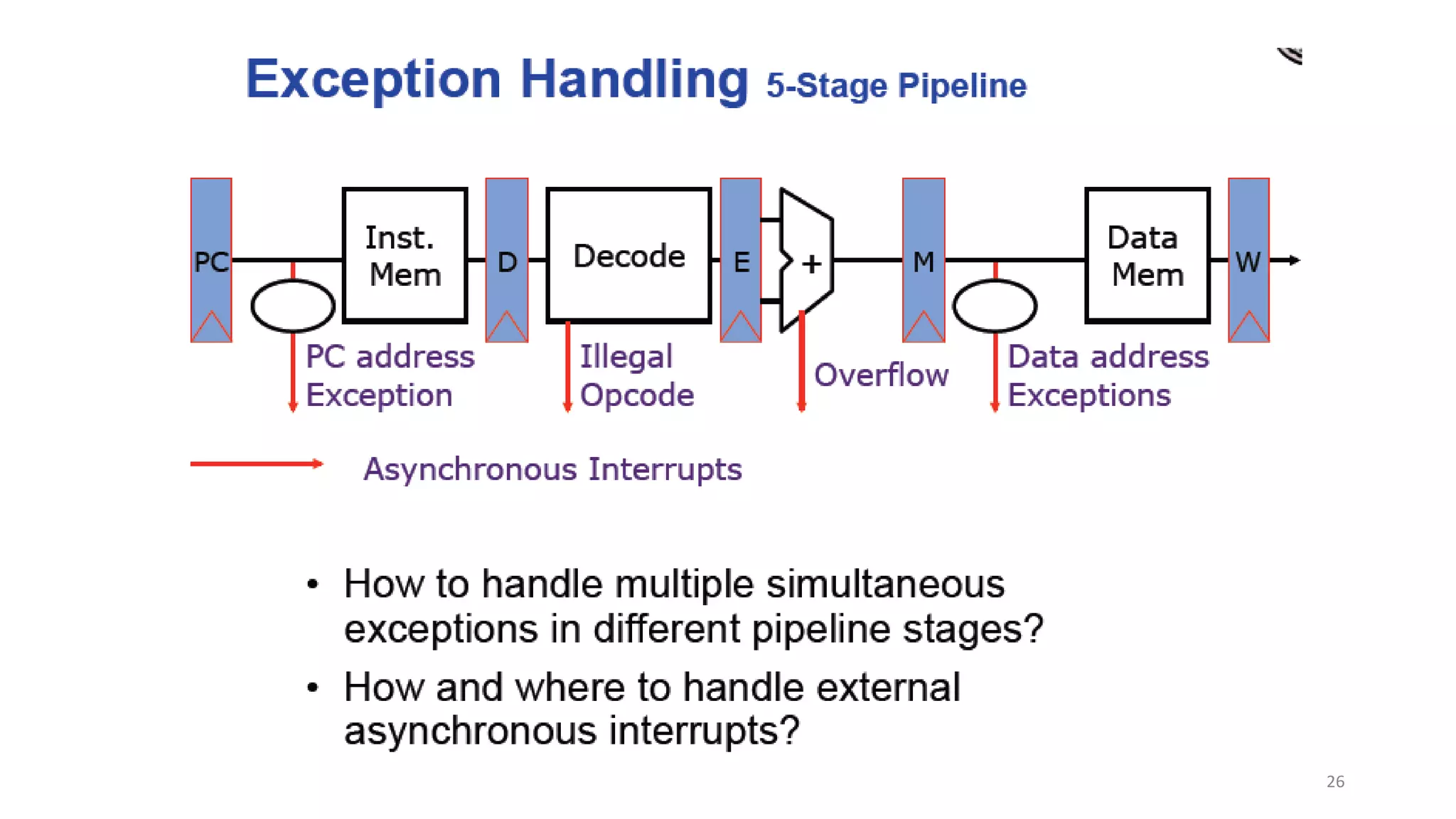

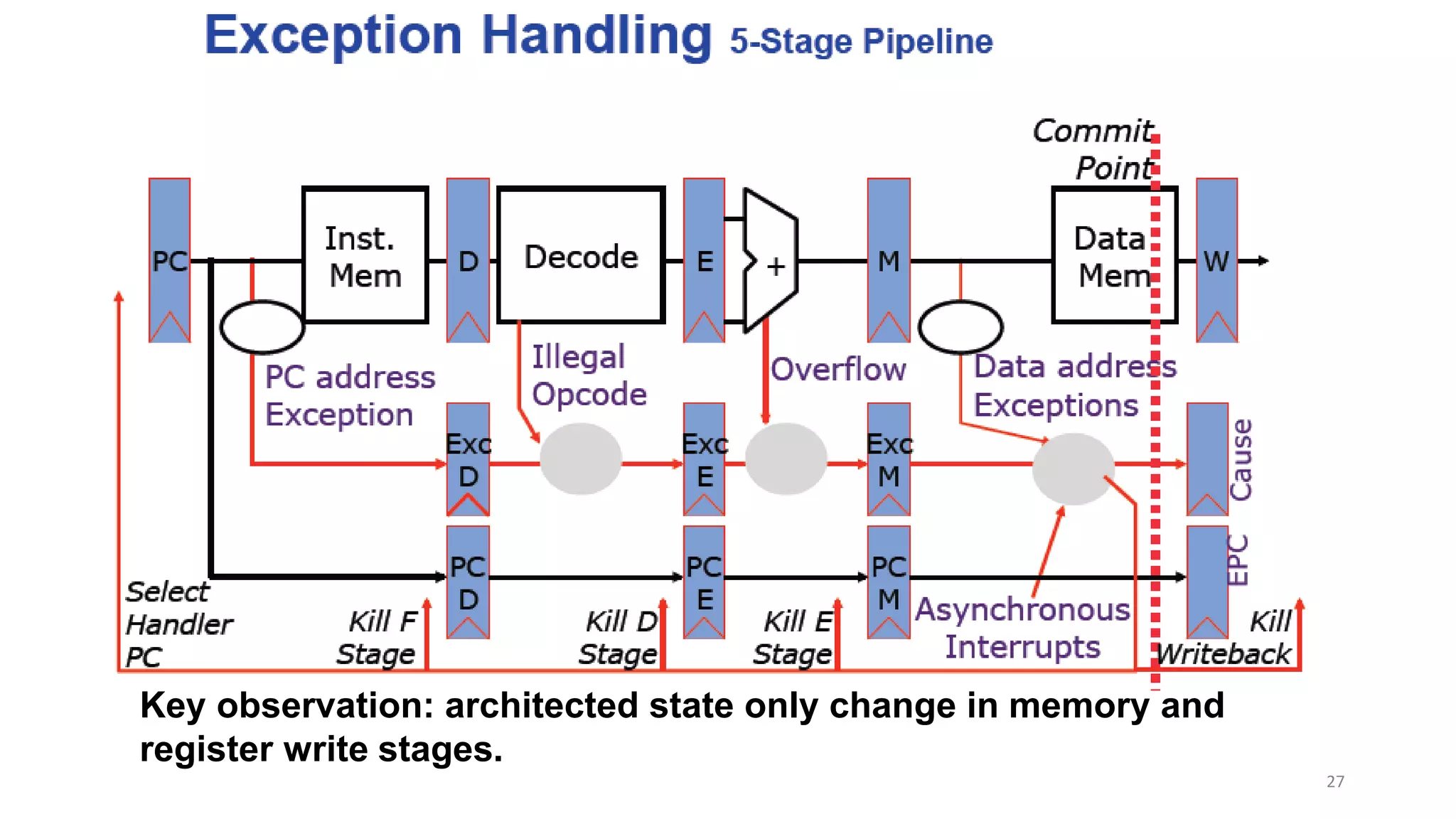

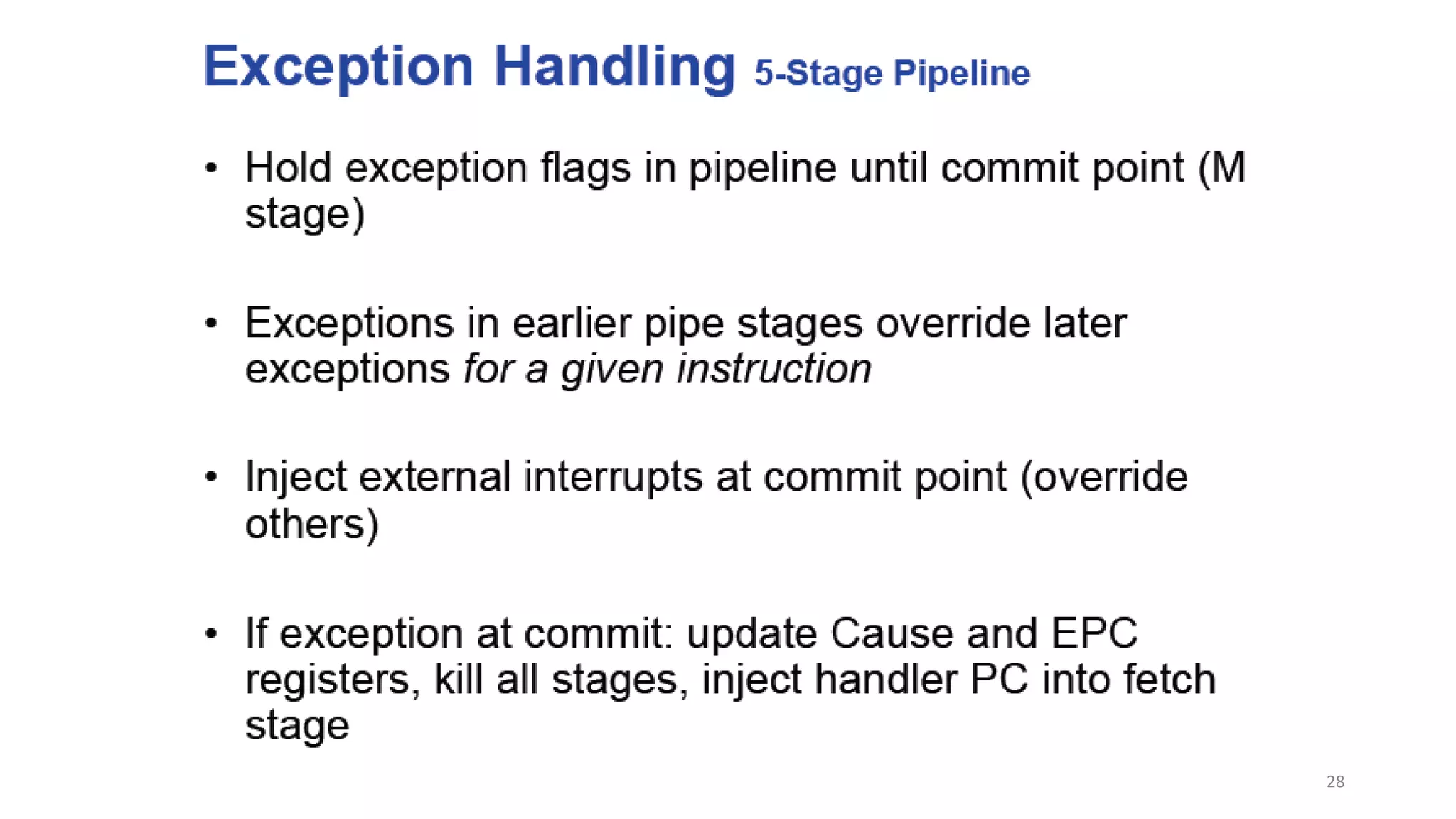

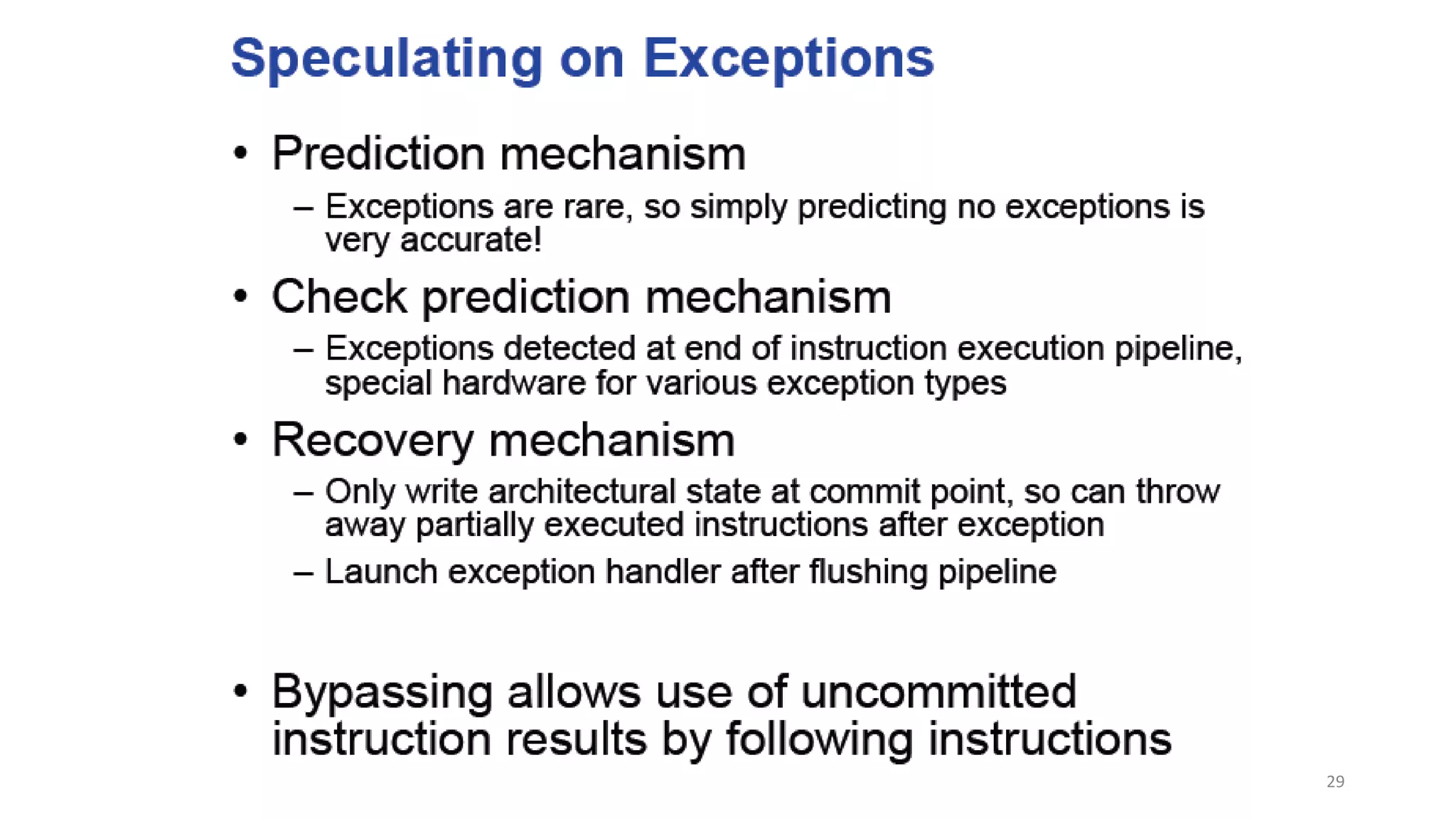

The document discusses exceptions in computer architecture. It describes two types of exceptions - interrupts and traps. Interrupts are caused by external events like I/O requests, while traps are caused by internal events like arithmetic overflow. When an exception occurs, the pipeline must stop executing the offending instruction, save state like the program counter, and jump to an exception handler. Handling exceptions in a pipelined processor is challenging as it can disrupt instruction flow. The document outlines some of the techniques used to handle exceptions in a pipeline, like writing exception information to registers and flushing instructions after the exception.

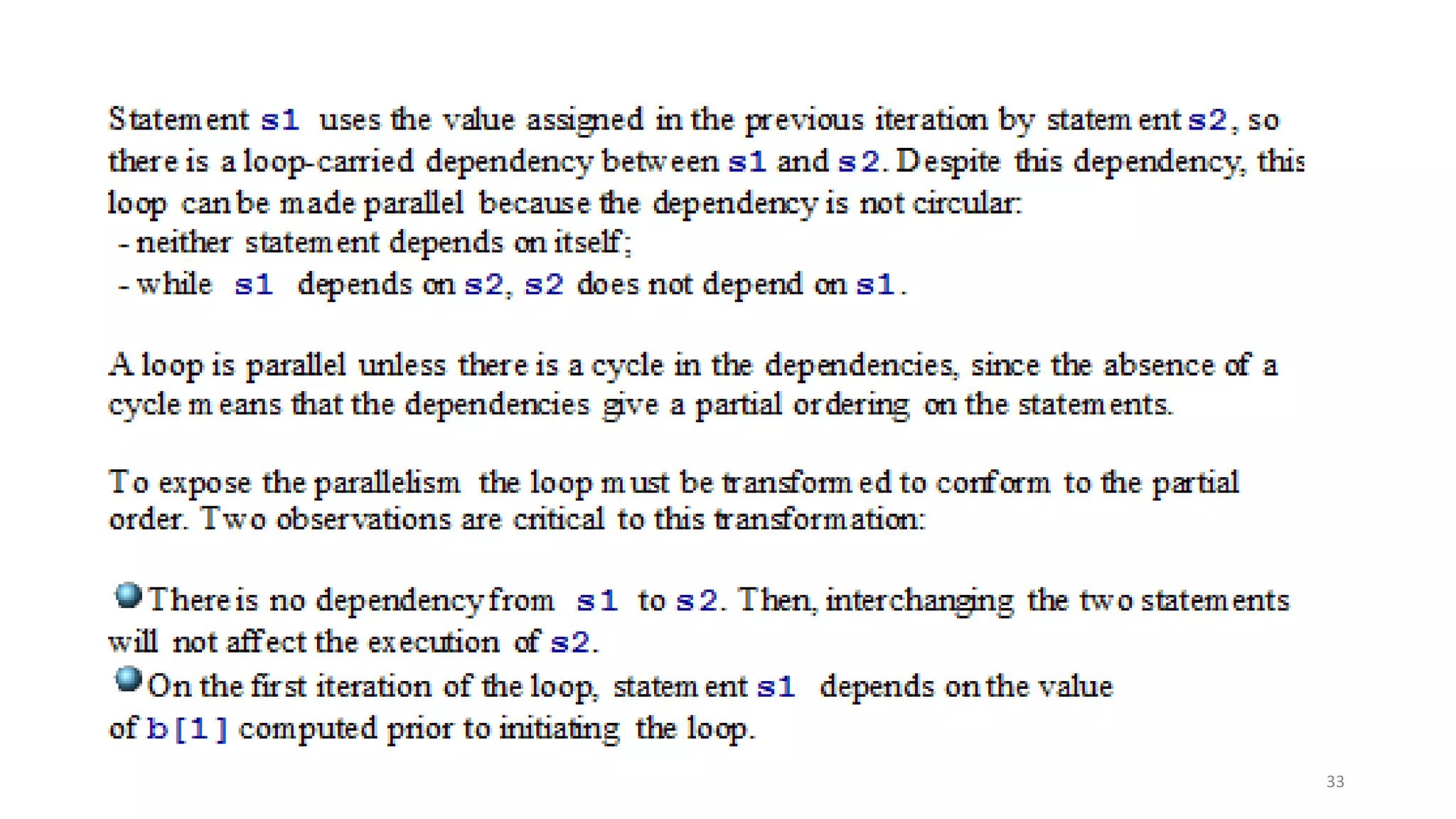

![34 This allows us to replace the loop above with the following code sequence, which makes possible overlapping of the iterations of the loop: a[1] = a[1] + b[1]; for (i=1; i<=99; i= i+1){ b[i+1] = c[i] + d[i]; a[i+1] = a[i+1] + b[i+1]; } b[101] = c[100] + d[100]; Example 3 for (i=1; i<=100; i= i+1){ a[i+1] = a[i] + c[i]; //S1 b[i+1] = b[i] + a[i+1]; //S2 } This loop is not parallel it has cycles in the dependencies, namely the statements S1 and S2 depend on themselves!](https://image.slidesharecdn.com/dealingwithexceptions-171231173625/75/Dealing-with-exceptions-Computer-Architecture-part-2-34-2048.jpg)