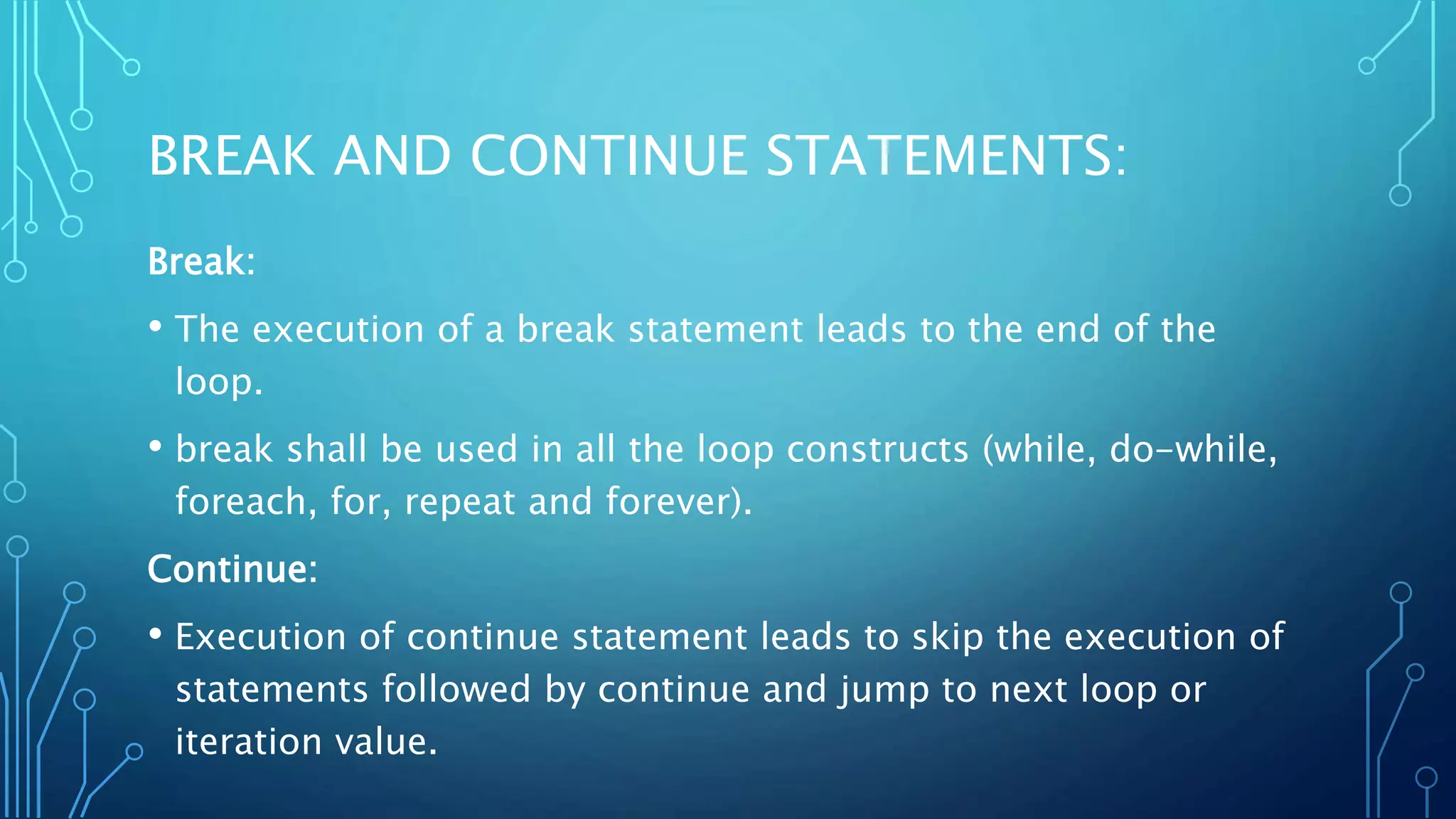

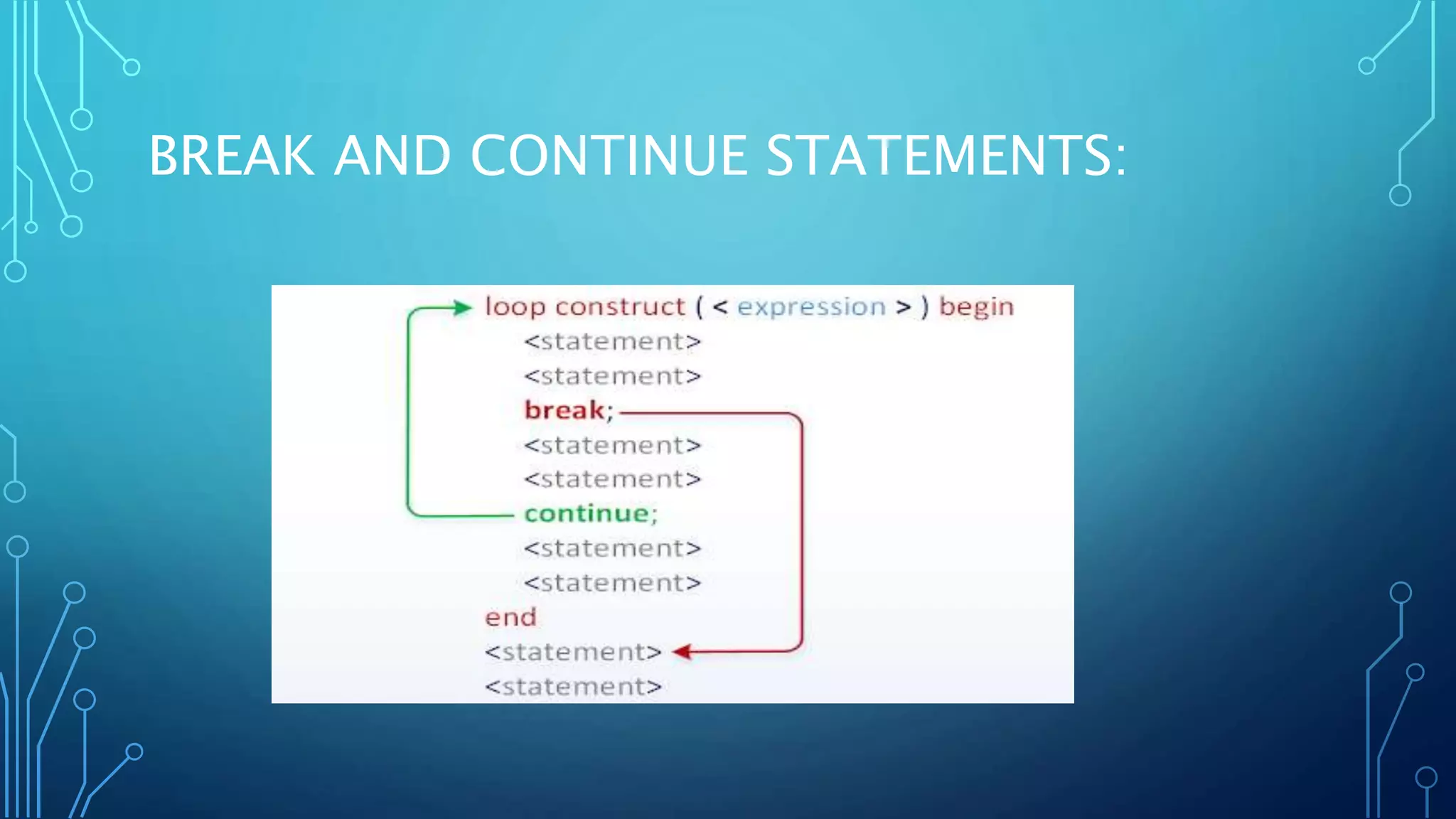

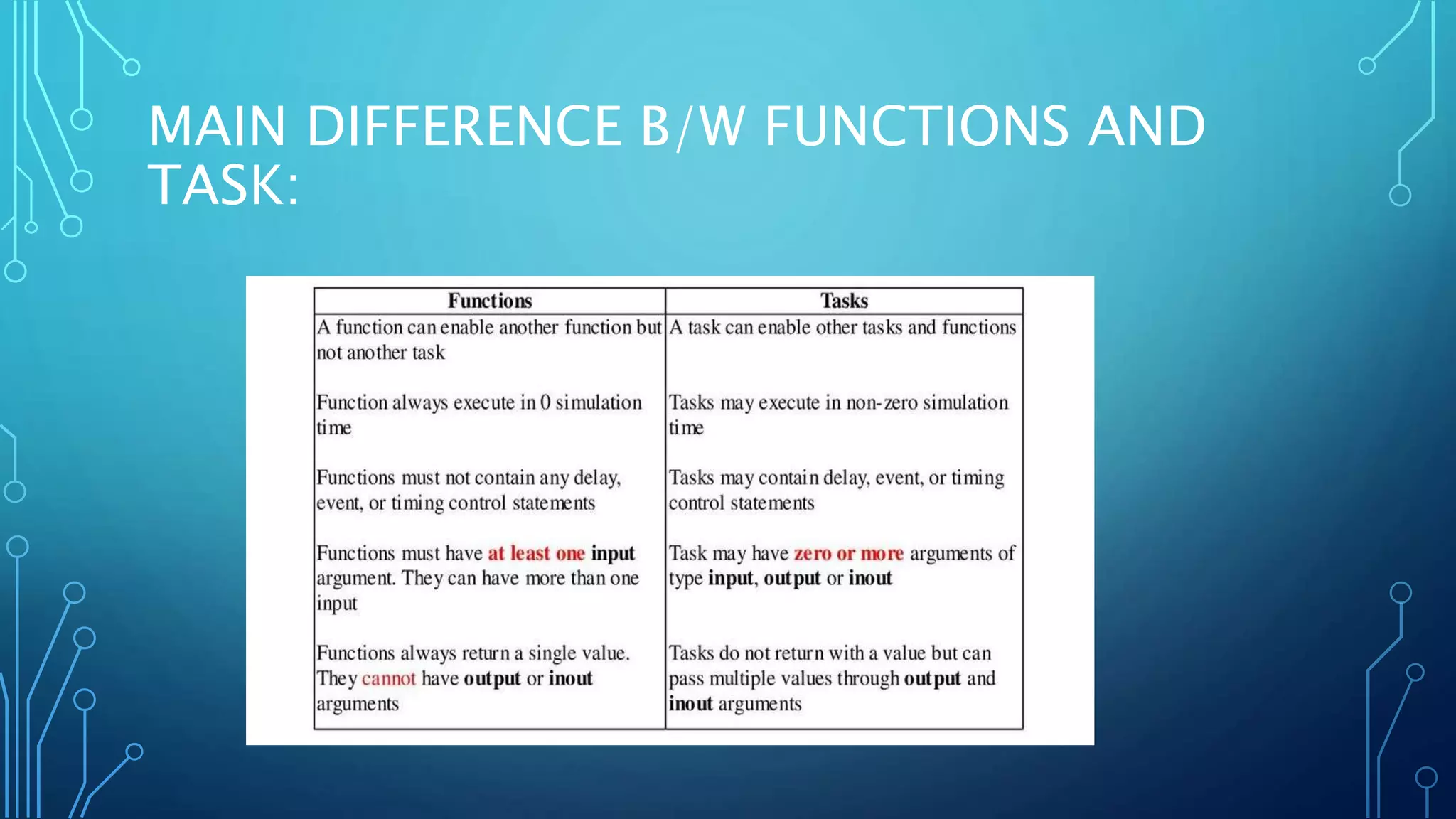

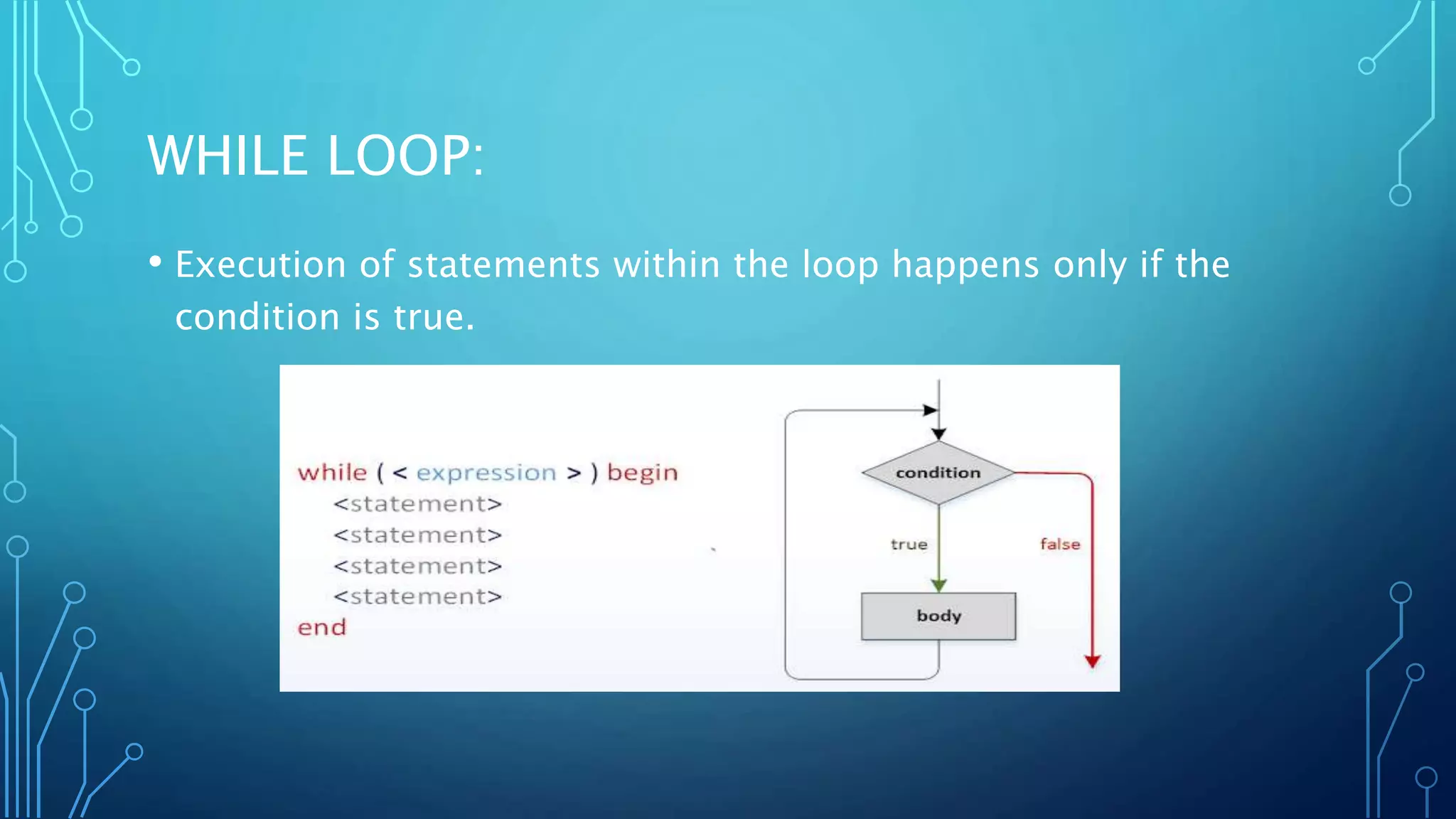

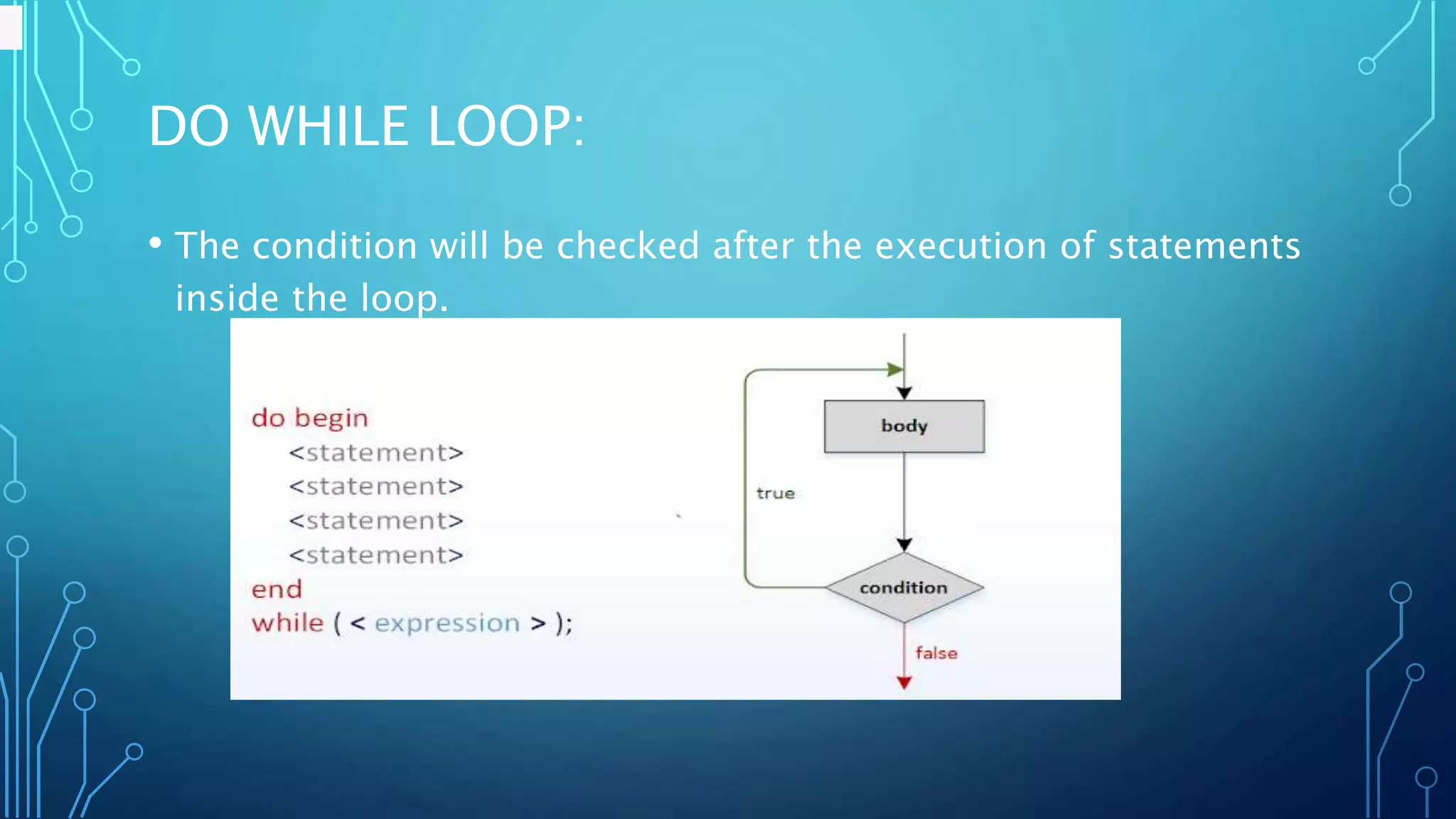

System Verilog introduces several new control flow constructs compared to Verilog, including unique if, priority if, foreach loops, and enhanced for loops. It also adds tasks and functions with arguments that can be passed by value, reference, or name. System Verilog defines two types of blocks - sequential blocks that execute statements sequentially and parallel blocks like fork-join that execute statements concurrently. It introduces various timing controls like delays, events, and wait statements.

![FOREACH LOOP: • System Verilog foreach specifies iteration over the elements of an array. • The loop variable is considered based on elements of an array and the number of loop variables must match the dimensions of an array. • Foreach loop iterates through each index starting from index 0. Syntax: foreach(<variable>[<iterator>]]) begin statement - 1 ... statement - n end](https://image.slidesharecdn.com/sv-controlflowbychinni2-201114055806/75/System-verilog-control-flow-9-2048.jpg)