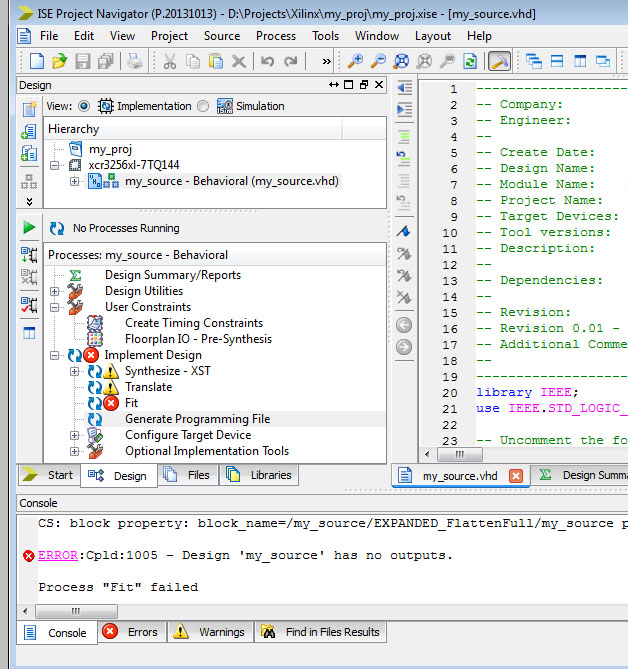

The Example project should contain the correct code.

This page indicates to open the jc2_abl project. This is found either by navigating to your ISEExamples directory in your ISE install (what they suggest you do, found in <Install Dir>/14.5/ISE_DS/ISE/ISEexamples), or by File -> Open Example.

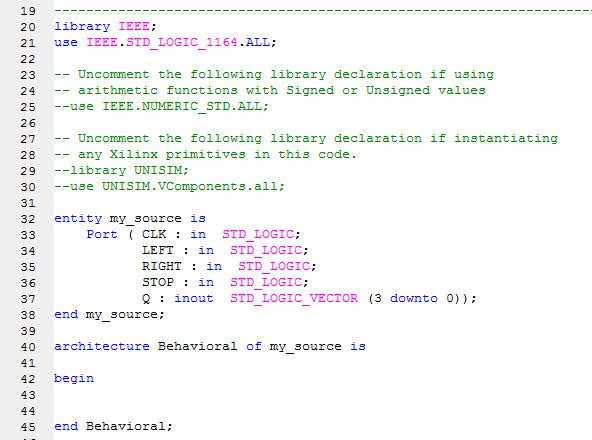

My particular install of ISE didn't have jc2_abl as an example, but did have jc2_vhd, which contains the vhd code for the example, copied here:

library IEEE; use IEEE.std_logic_1164.all; -- defines std_logic types entity jc2_top is port ( left : in std_logic; -- Active-low switch #3 (left) right : in std_logic; -- Active-low switch #0 (right) STOP : in std_logic; -- Active-low switch #2 CLK : in std_logic; Q : out std_logic_vector (3 downto 0) -- Active-low LEDs ); --To pass pin location constraints from this HDL source file rather than --through a User Constraints Format (UCF) file, uncomment the six attribute --declarations below and remove jc2_top.ucf from the project. -- attribute pin_assign : string; -- attribute pin_assign of clk : signal is "A7"; -- attribute pin_assign of left : signal is "G7"; -- attribute pin_assign of right : signal is "B2"; -- attribute pin_assign of stop : signal is "F2"; -- attribute pin_assign of q : signal is "G5 F6 C6 B4"; end jc2_top; architecture jc2_top_arch of jc2_top is signal DIR : std_logic := '0'; -- Left=1, Right=0 signal RUN : std_logic := '0'; signal Q_int : std_logic_vector (3 downto 0) := "0000"; -- Internal signal driving Q output; Active-low LEDs begin process (CLK, right, left, STOP, RUN, DIR, Q_int) begin if (CLK'event and CLK = '1') then -- CLK rising edge -- DIR register: if (right = '0') then DIR <= '0'; elsif (left = '0') then DIR <= '1'; end if; -- RUN register: if (STOP = '0') then RUN <= '0'; elsif (left = '0' or right = '0') then RUN <= '1'; end if; -- Counter section: if (RUN = '1') then if (DIR = '1') then Q_int(3 downto 1) <= Q_int(2 downto 0); -- Shift lower bits (Left Shift) Q_int(0) <= not Q_int(3); -- Circulate inverted MSB to LSB else Q_int(2 downto 0) <= Q_int(3 downto 1); -- Shift upper bits (Right Shift) Q_int(3) <= not Q_int(0); -- Circulate inverted LSB to MSB end if; end if; end if; Q <= Q_int; end process; end jc2_top_arch;